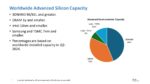

Throughout the debate on fab incentives and the Chips Act I keep seeing comments like; TSMC makes >90% of all advanced silicon, or sometimes Taiwan make >90% of all advanced silicon. This kind of ill-defined and grossly inaccurate statement drives me crazy. I just saw someone make that same claim in the SemiWiki forums and… Read More

Intel and TSMC IDM 2024 Discussions

In December 2023, we published the Intel Revenue forecast for external wafer sales, gave a breakdown on how customers plan to ramp the foundry. The forecast is still valid (it assumes Intel executes on all plans) but since then we have a better understanding of Intel’s strategy and scenarios that could unfold.

The scenarios… Read More

ISS 2024 – Logic 2034 – Technology, Economics, and Sustainability

For the 2024 SEMI International Strategy Symposium I was challenged by members of the organizing committee to look at where logic will be in ten years from a technology, economics, and sustainability perspective. The following is a discussion of my presentation.

To understand logic, I believe it is useful to understand what makes… Read More

How Disruptive will Chiplets be for Intel and TSMC?

Chiplets (die stacking) is not new. The origins are deeply rooted in the semiconductor industry and represent a modular approach to designing and manufacturing integrated circuits. The concept of chiplets has been energized as a response to the recent challenges posed by the increasing complexity of semiconductor design. … Read More

2024 Big Race is TSMC N2 and Intel 18A

There is a lot being said about Intel getting the lead back from TSMC with their 18A process. Like anything else in the semiconductor industry there is much more here than meets the eye, absolutely.

From the surface, TSMC has a massive ecosystem and is in the lead as far as process technologies and foundry design starts but Intel is … Read More

IEDM: TSMC Ongoing Research on a CFET Process

I attended the recent International Electron Devices Meeting (IEDM) last week. Many of the sessions are too technical and too far away from high volume manufacture to make good topics for a blog post. As a Fellow from IBM said about 5nm at and earlier IEDM, “none of these ideas will impact 5nm. It takes ten years for a solution to from… Read More

Arm Total Design Hints at Accelerating Multi-Die Activity

I confess I am reading tea leaves in this blog, but why not? Arm recently announced Arm Total Design, an expansion of their Compute Subsystems (CSS) offering which made me wonder about the motivation behind this direction. They have a lot of blue-chip partners lined up for this program yet only a general pointer to multi-die systems… Read More

Analog Bits Leads the Way at TSMC OIP with High-Accuracy Sensors

The 15th TSMC Open Innovation Platform® (OIP) event was held recently. This event is a focal point across the industry for cutting-edge development and industry-level collaboration. Appropriately, advanced packaging, paving the way for multi-die design was a focal point for the event. You can get a good overview of what was … Read More

TSMC N3E is ready for designs, thanks to IP from Synopsys

TSMC has been offering foundry services since 1987, and their first 3nm node was called N3 and debuted in 2022; now they have an enhanced 3nm node dubbed N3E that has launched. Every new node then requires IP that is carefully designed, characterized and validated in silicon to ensure that the IP specifications are being met and … Read More

The True Power of the TSMC Ecosystem!

The 15th TSMC Open Innovation Platform® (OIP) was held last week. In preparation we did a podcast with one of the original members of the TSMC OIP team Dan Kochpatcharin. Dan and I talked about the early days before OIP when we did reference flows together. Around 20 years ago I did a career pivot and focused on Strategic Foundry Relationships.… Read More