In the relentless race to power next-generation artificial intelligence (AI) systems, data connectivity has emerged as the critical bottleneck. As AI models balloon in size—from billions to trillions of parameters—compute resources alone are insufficient. According to Ayar Labs, approximately 70% of AI compute time is … Read More

Analog Bits Steps into the Spotlight at TSMC OIP

The TSMC Open Innovation Platform (OIP) Ecosystem Forum kicked off on September 24 in Santa Clara, CA. This is the event where TSMC recognizes and promotes the vast ecosystem the company has created. After watching this effort grow over the years, I feel that there is nothing the group can’t accomplish thanks to the alignment and… Read More

Synopsys Collaborates with TSMC to Enable Advanced 2D and 3D Design Solutions

Synopsys has deepened its collaboration with TSMC certifying the Ansys portfolio of simulation and analysis tools for TSMC’s cutting-edge manufacturing processes including N3C, N3P, N2P, and A16. This partnership empowers chip designers to perform precise final checks on designs, targeting applications in AI acceleration,… Read More

TSMC’s Push for Energy-Efficient AI: Innovations in Logic and Packaging

In his keynote at the TSMC OIP Ecosystem Forum Dr. LC Lu, TSMC Senior Fellow and Vice President, Research & Development / Design & Technology Platform, highlighted the exponential rise in power demand driven by AI proliferation. AI is embedding itself everywhere, from hyperscale data centers to edge devices, fueling… Read More

MediaTek Develops Chip Utilizing TSMC’s 2nm Process, Achieving Milestones in Performance and Power Efficiency

MediaTek’s first chipset using 2nm technology expected in late 2026

MediaTek, a global leader in fabless semiconductor design, has announced a groundbreaking achievement in its partnership with TSMC. The company has successfully developed a flagship system-on-chip (SoC) utilizing TSMC’s cutting-edge 2nm process technology,… Read More

TSMC’s 2024 Sustainability Report: Pioneering a Greener Semiconductor Future

TSMC, the world’s most trusted semiconductor foundry, released its 2024 Sustainability Report, underscoring its commitment to embedding environmental, social, and governance principles into its operations. Founded in 1987 and headquartered in Hsinchu Science Park, TSMC employs 84,512 people globally and operates… Read More

TSMC 2025 Update: Riding the AI Wave Amid Global Expansion

Welcome to the second half of a very exciting year in semiconductors. While Intel and Samsung Foundry have made quite a few headlines, TSMC continues to execute flawlessly at 3nm and 2nm. With the TSMC OIP Ecosystem Forums starting later this month let’s take a look at how we got to where we are today.

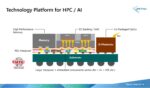

Alchip Launches 2nm Design Platform for HPC and AI ASICs, Eyes TSMC N2 and A16 Roadmap

Alchip Technologies, a global leader in high-performance computing (HPC) and AI infrastructure ASICs, has officially launched its 2nm Design Platform, marking a major advancement in custom silicon design. The company has already received its first 2nm wafers and is collaborating with customers on the development of high-performance… Read More

Certus Semiconductor at the 2025 Design Automation Conference #62DAC

Certus Semiconductor Brings High-Performance Custom I/O and ESD IP to DAC 2025

Certus Semiconductor, a trusted leader in custom I/O and ESD solutions, will exhibit at booth #1731 during DAC 2025, June 23–27 in San Francisco. Known for its robust, customer-proven IP tailored for challenging applications, Certus will highlight… Read More

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More