If you don’t know about Karen Bartleson, before I get into details, let me tell you that she was the President of IEEE-SA for the past 2 years and has been nominated by the IEEE Board of Directors as one of the candidates for IEEE President-Elect for 2016. The IEEE is an organization I admire as it plays a key role in advancing technology… Read More

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

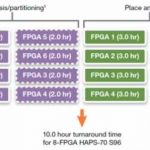

More FPGA-based prototype myths quashed

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

John Koeter: How To Be #1 in Interface IP

John Koeter is in charge of marketing Synopsys’ IP and prototyping solutions. I talked to him last week.

He grew up in upstate New York, son of a Scottish mother and a Dutch father who immigrated to the US, so he is first generation American, unlike everyone else I’ve interviewed so far for this series who were born overseas.… Read More

I want to use USB Type C (and I want it now)

USB is certainly the most ubiquitous of the Interface protocols, used in our day to day life to connect multiple systems, as well as in professional segments like industrial or even high performance servers (yes, these systems integrates USB 3 connections). But USB is also one of the protocols able to generate frustration every… Read More

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

Synopsys’ Andreas Kuehlmann on Software Development

Andreas Kuehlmann is the general manager of what is officially now known as the Software Integrity Group of Synopsys, what you might think of as Coverity although they have made some acquisitions too, so they now have a broader technology base. I sat down to talk to him last week.

He was brought up in Germany and came to the US in 1991 … Read More

Synopsys Buys Bluetooth IP

There is obviously a broad spectrum of semiconductor IP but broadly speaking it seems to fall into three buckets:

- foundation IP: standard cells, memories

- microprocessors and associated peripherals

- interface IP

Foundation IP is where it all started. When I was at Compass Design Automation in the 1990s that was pretty much what… Read More

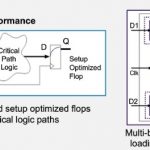

Antun Domic, on Synopsys’ Secret Sauce in Design

Antun Domic is the GM of the Design Group at Synopsys. I sat down with him a couple of weeks ago.

His name is Croatian although, of course, there was no Croatia back then it was part of Yugoslavia. But in fact he grew up in Chile and went to university there where he studied EE and math. He came to the US as a grad student and did a PhD at MIT in … Read More

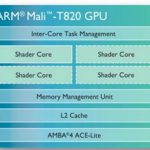

How ARM Implemented a Mali GPU using Logic Synthesis and Place/Route Tools

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More