As SoC and IP designs continue to increase in complexity while schedules accelerate, verification teams are looking for methodologies to improve design confidence more quickly. Formal verification techniques provide one route to improved design confidence, and the increase in papers and interest at industry conferences… Read More

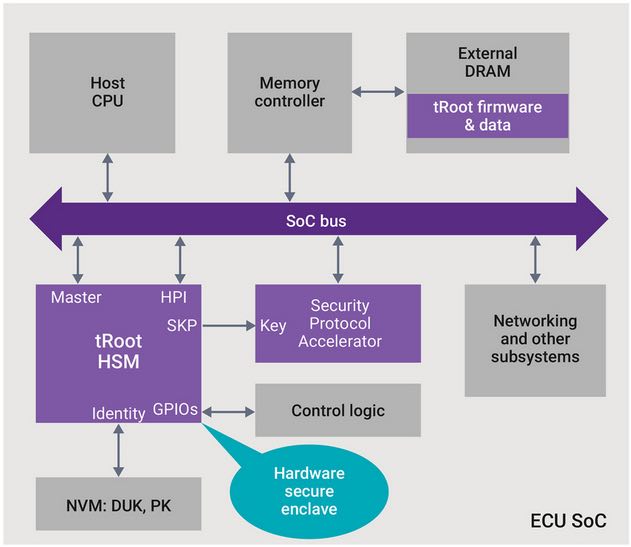

Car Vandals Eschew Crowbars

It used to be that automotive theft and crime was perpetrated with a crowbar. Now with increased electronics content, car designer and owners need to worry about electronic threats. Anywhere there is a communication link or a processor, there are potential threats to the security of the car. The range of these threats covers everything… Read More

Design Compiler – Next Generation

Back in 1986, Synopsys started out with a synthesis product by name of SOCRATES, which stands for Synthesis andOptimization ofCombinatorial logic usingRule-basedAndTechnology independentExpertSystem. It is fair to say that not many designers know that was the birth name of what eventually turns out to be a very successful… Read More

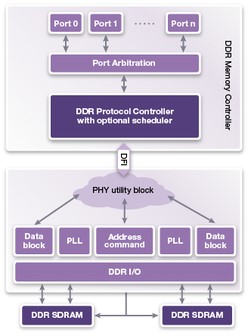

Synopsys DDR5 LPDDR5 Memory Interface IP Targets AI, Automotive, and Mobile SoCs

Synopsys announced on October 24 new DesignWare[SUP]®[/SUP] Memory Interface IP solutions supporting the next-generation DDR5 and LPDDR5 SDRAMs. The DDR5 and LPDDR5 IP significantly increase memory interface bandwidth compared to DDR4 and LPDDR4/4X SDRAM interfaces, while reducing area and improving power efficiency.… Read More

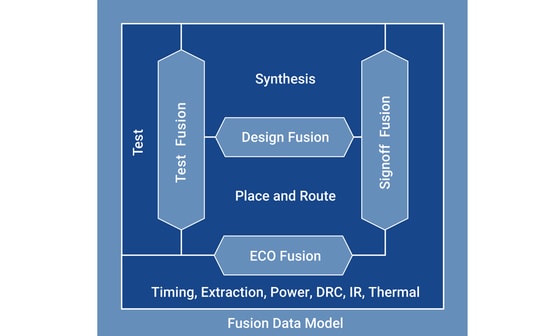

Fusion Synthesis for Advanced Process Nodes

Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited… Read More

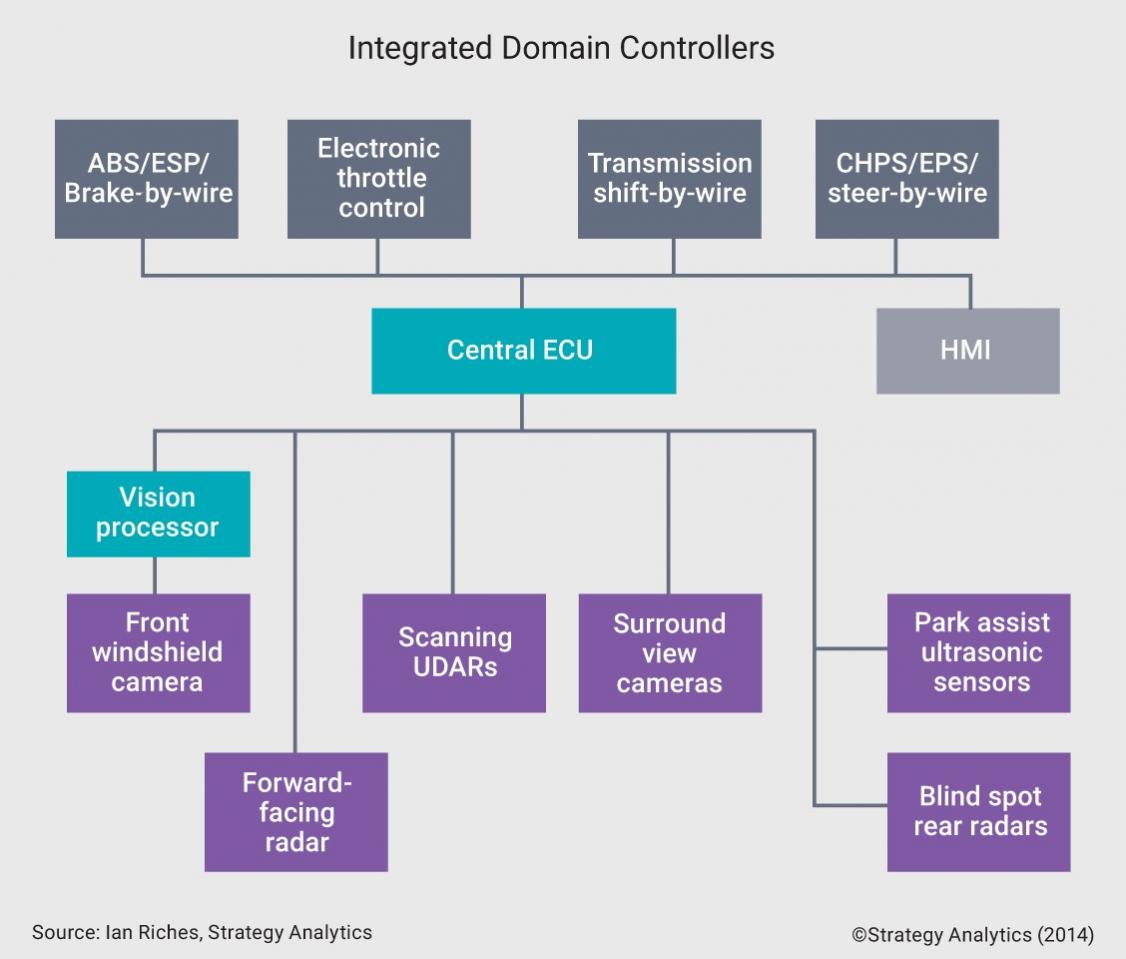

Designing Integrated ADAS Domain Controller SoCs with ISO 26262 Certified IP

As new automotive Advanced Driver Assistance System (ADAS) based product releases intensifies while a more stringent set of safety requirements are mandated, it is not surprising that subsystem and electronic suppliers are looking for pre-designed and ISO 26262 certified IP that can address both imperatives of schedule and… Read More

TSMC and Synopsys are in the Cloud!

EDA has been flirting with the cloud unsuccessfully for many years now and it really comes down to a familiar question: Who can afford to spend billions of dollars on data center security? Which is similar to the question that started the fabless transformation: Who can afford to spend billions of dollars on semiconductor manufacturing… Read More

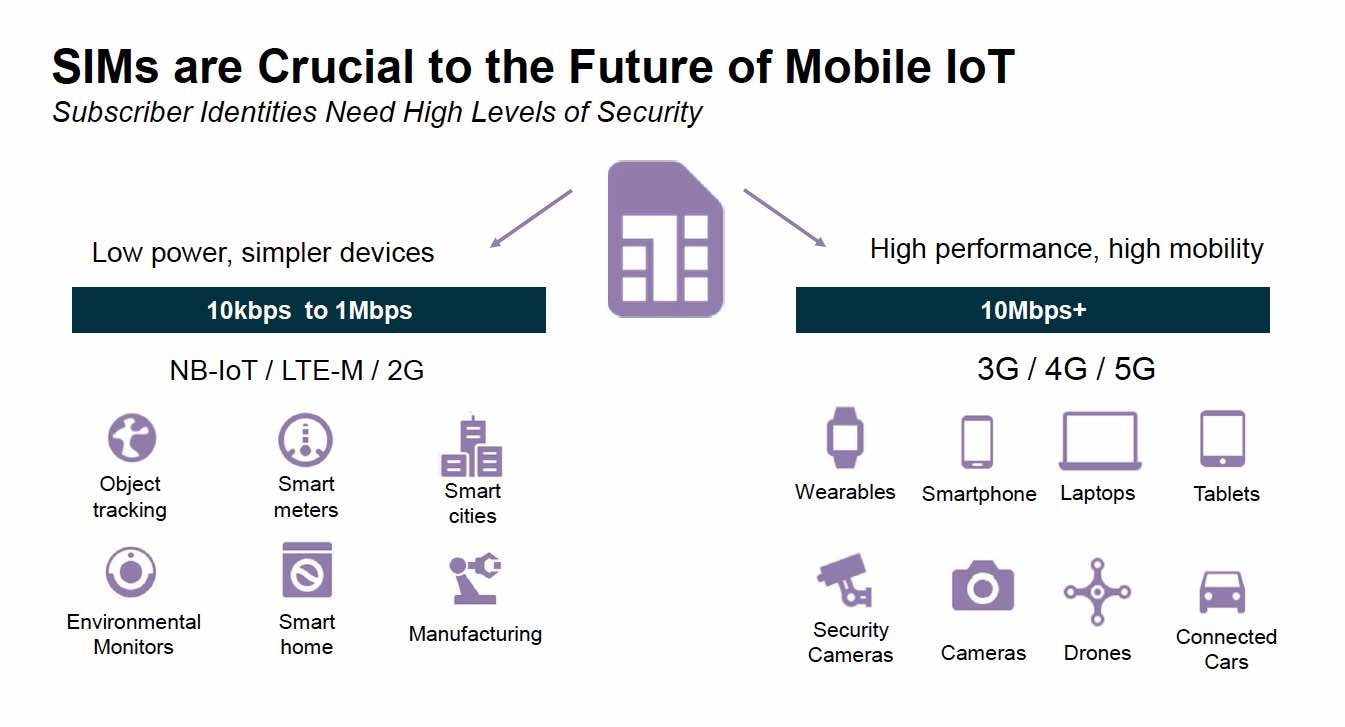

Synopsys Seeds Significant SIM Segue

It turns out that consumers are not alone in their love-hate relationship with SIM cards. SIM cards save us from increasingly widespread cellphone cloning. However, if your experience is anything like mine, it seemed that with every new phone, a new SIM card format was needed. Furthermore, people travelling overseas who wanted… Read More

DesignWare IP as AI Building Blocks

AI is disruptive and transformative to many status quos. Its manifestation can be increasingly seen in many business transactions and various aspects of our lives. While machine learning (ML) and deep learning (DL) have acted as its catalysts on the software side, GPU and now ML/DL accelerators are spawning across the hardware… Read More

A Closer Look at Fusion from Synopsys at #55DAC

Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar … Read More