You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

Semiconductor IP is one of the most talked about topics on SemiWiki. Always has been, always will be. Synopsys is also one of the most talked about topics on SemiWiki and IP is a very big part of that, absolutely.

After reading Eric Esteve’s latest IP Report I Googled around and found some interesting things. First, I found a Brief History… Read More

Many of us are now somewhat fluent in IoT-speak, though at times I have to wonder if I’m really up on the latest terminology. Between edge and extreme edge, fog and cloud, not to mention emerging hierarchies in radio access networks – how this all plays out is going to be an interesting game to watch. Ron Lowman, DesignWare IP Product… Read More

Back in my Atrenta days (before mid-2015), we were already running into a lot of very large SoC-level designs – a billion gates or more. At those sizes, full-chip verification of any kind becomes extremely challenging. Memory demand and run-times explode, and verification costs explode also since these runs require access to … Read More

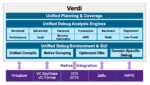

Want fast debug? Synopsys recently hosted a Webinar to show off the latest and greatest improvements to Verdi® in performance, memory demand and multi-tasking, among other areas.

Performance improvements

Taruna Reddy (PMM) and Allen Hsieh (Staff apps) presented features of the latest version, released in March – Taruna started… Read More

Summary

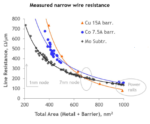

Design Technology Co-Optimization (DTCO) analysis was pursued for library cell PPA estimates for gate-all-around (GAA) devices and new metallurgy options. The cell design and process recommendations are a bit surprising.

Introduction

During the “golden years” of silicon technology evolution that applied Dennard… Read More

I had the opportunity to preview an upcoming webinar from Synopsys on SoC Glitch Power – what it is and how to reduce it. There is some eye-opening information in this webinar. Glitch power is a bigger problem than you may think and Synopsys has some excellent strategies to help reduce the problem. The webinar is available via replay… Read More

Synopsys announced an addition to its popular DesignWare IP portfolio recently that has some significant ramifications. The company announced the industry’s first complete USB4 IP solution. Before we get into the details of the announcement, let’s take a quick look at the USB standard and why it’s important.

Standards… Read More

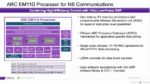

If you are like me, you will get a 5G phone because of the high bandwidth it offers. However, there is a lot more to 5G than just fast data. In fact, one of the appealing features of 5G is low bandwidth communication. This is useful for edge devices that perform infrequent and low volume data transfers and depend on long battery life. Prior… Read More

Design complexities in reset, like everything else in big SoC designs, has become incredibly complex, for all sorts of reasons. Long, long ago reset was something you just did once, when you turned the power on. Turn on, then hold reset for some amount of time until everything is in a known starting state, and off you go. Nice and simple.… Read More

About 90 days ago, Synopsys completed the acquisition of certain IP assets from eSilicon. The remaining entirety of eSilicon was acquired by Inphi Corporation. I was the VP of marketing at eSilicon during that acquisition so it’s very interesting to me to find out how things are going with those certain IP assets. I got an opportunity… Read More