If you ascribe to the notion that things move in circles, or concentrically, the move to die-to-die connectivity makes complete sense. Just as multi-chip modules (MCM) were the right technology decades ago to improve power, areas, performance and cost, the use of chiplets with die-to-die connections provides many advantages… Read More

IoT’s Inconvenient Truth: IoT Security Is a Never-Ending Battle

The continued innovation and widespread adoption of connected devices — the internet of things (IoT) — has resulted in a vast range of conveniences that improve our lives every day. At the same time, the ubiquity of IoT devices, which market watchers estimate to be in the tens of billions, also makes it more attractive to bad actors… Read More

Upping the Safety Game Plan for Automotive SoCs

Thanks to advanced hardware and software, smart vehicles are improving with every generation. Capabilities that once seemed far-off and futuristic—from automatic braking to self-driving at the very pinnacle—are now either standard or within reach. However, considering how vehicle architectures have continued to evolve,… Read More

Mars Perseverance Rover Features First Zoom Lens in Deep Space

On July 30, 2020, NASA launched the Mars 2020 Perseverance rover, which is scheduled to land today. Perseverance has been deployed to Mars with a new mission: to search for evidence of past life and collect samples that will eventually be brought back to Earth by future missions.

Verification Management the Synopsys Way

Remember the days when verification meant running a simulator with directed tests? (Back then we just called them tests.) Then came static and formal verification, simulation running in farms, emulation and FPGA prototyping. We now have UVM, constrained random testing and many different test objectives (functional, power,… Read More

Synopsys Debuts Major New Analog Simulation Capabilities

Just prior to this year’s Synopsys User Group (SNUG) meeting, I had a call with Hany Elhak, Group Director of Product Management and Marketing at Synopsys, to talk about their latest announcements for analog simulation. Synopsys usually has big things to talk about each year around this time – this year is no exception. Hany… Read More

Accelerating Cache Coherence Verification

It would be nice if there were a pre-packaged set of assertions which could formally check all aspects of cache coherence in an SoC. In fact, formal checks do a very nice job for the control aspects of a coherent network. But that covers only one part of the cache coherence verification task. Dataflow checks are just as important, where… Read More

PCIe 6.0 Doubles Speed with New Modulation Technique

PCI-SIG has held to doubling PCIe’s data rate with each revision of the specification. The consortium of 800 companies, with its board consisting of Agilent, AMD, Dell, HP, Intel, Synopsys, NVIDIA, and Qualcomm, is continuing this trend with the PCIe 6.0 specification which calls for a transfer rate of 64 GT/s. PCI-SIG released… Read More

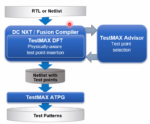

Addressing SoC Test Implementation Time and Costs

In business we all have heard the maxim, “Time is Money.” I learned this lesson early on in my semiconductor career when doing DRAM design, discovering that the packaging costs and time on the tester were actually higher than the fabrication costs. System companies like IBM were early adopters of Design For Test (DFT)… Read More

Your Car Is a Smartphone on Wheels—and It Needs Smartphone Security

Your modern car is a computer on wheels—potentially hundreds of computers on a set of wheels. Heck, even the wheels are infested with computers—what do you think prompts that little light on your dashboard to come on if your tire pressure is low? And computers don’t just run your infotainment system, backup camera, dashboard warning