Ever since the “Intel Reinvents Transistors Using New 3-D Structure” PR campaign I have been at odds with them. As technologists, I have nothing but respect for Intel. The Intel PR department, however, quite frankly, is evil. Correct me if I’m wrong here but Intel did not “reinvent” the transistor. Nor did they come up with the name… Read More

TSMC Update 2012!

TSMC has had an interesting year thus far. 28nm is ramped and will dominate the mobile market for years to come. 20nm is in development with tape outs scheduled for the end of this year. FinFETS are coming making it a very exciting time in the semiconductor ecosystem. … Read More

Intel’s Tri-Gate May Have Moore Problems Than You Think!

Clever title but it’s not mine. Piper Jaffray Analysts Auguste Richard and Jennifer Baxter released a report last week which echoed the concerns of others, including myself. The concerns reported are with the 22nm process and not the chipsets themselves. To me this is all part of ramping a leading edge process but the concerns are… Read More

Semiconductor Ecosystem Keynotes: ARM 2012

Yesterday’s SEMICO IP Ecosystem Conference was well worth the time. Everybody was there: ARM, Synopsys, Cadence, Mentor Graphics, GlobalFoundries, TSMC, MIPS, Tensilica, AMD, Atrenta, Sonics, and Tabula, everybody except Intel of course. What do Intel and I have in common? We don’t play well with others…

First up was… Read More

TSMC Tops Intel, Samsung in Capacity!

While I was marlin fishing in Hawaii last week I missed some interesting comments from TSMC executives at the Technology Symposium in Taiwan, a much different show than the one here in San Jose I’m told. It is good to see TSMC setting the record straight and taking a little credit for what they have accomplished! I’m sorry I missed it… Read More

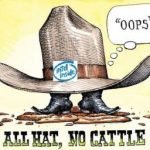

Intel Foundry All Hat No Cattle?

If you look real close at the #49 DAC floor plan you will see the tiny Intel booth dwarfed by those of TSMC, GlobalFoundries, Samsung, and ARM. The number one semiconductor company in the world does not have the budget for the cornerstone conference of the semiconductor ecosystem? Oh my…… Intel has a big foundry hat and no cattle… Read More

TSMC 20nm Challenges!

Now that the 28nm challenges are dead

It is time to look ahead

The tabloid pundits may not agree

But Moore’s law again you will see

The semiconductor ecosystem is humming

(2X gate density -20%+ performance-20%+ power savings)

The 20nm design starts are coming!

Okay, I’m really bad at poetry. Gambling however, I do pretty well. Las… Read More

IC design at 20nm with TSMC and Synopsys

While the debate rages on about 28nm yield at foundry juggernaut TSMC, on Monday I attended a webinar on 20nm IC design hosted by TSMC and Synopsys. Double Patterning Technology (DPT) becomes a requirement for several layers of your 20nm IC design which then impact many of your EDA tools and methodology.… Read More

Intel says fabless model collapsing… really?

There is an interesting discussion in the SemiWiki forum in response to the EETimes article: Intel exec says fabless model ‘collapsing’. Definitely an interesting debate, one worth our time since the advertising click hungry industry pundits will certainly jump all over it. Clearly I’m biased since I helped build… Read More

TSMC 28nm Beats Q1 2012 Expectations!

TSMC just finished theQ1 conference call. I will let the experts haggle over the wording of the financial analysis, but the big news is that TSMC 28nm Q1 revenue was 5%, beating my guess of 4%. So all of you who bet against TSMC 28nm it’s time to pay up! Coincidentally, I’m in Las Vegas where the term deadbeat is taken literally!

Per my … Read More