I mentioned a while back that I’m really getting into the role that sensors play in our new hyper-connected world – in the IoT, intelligent cars, homes, cities, industry, utilities, medicine, agriculture, etc, etc. If we can think of a way to sense it and connect it, someone is probably already doing it. But there’s more to … Read More

FPGA based Prototyping

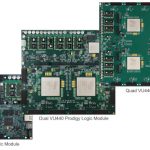

S2C Delivers FPGA Prototyping Solutions with the Industry’s Highest Capacity FPGA from Intel!

In 2016 we published our book “Prototypical: The Emergence of FPGA-Based Prototyping for SoC Design” which began an incredible journey through ASIC prototyping. While we are working on an update to that book there is some recent Prototyping news that is worthy of praise.

First and foremost, S2C Inc. has just announced THE single… Read More

Cadence and Green Hills Share More Security Thoughts at ARM Techcon

On Wednesday, October 9, 2019, I had the pleasure of spending the day at ARM Techcon at the San Jose Convention Center. In the morning, in addition to getting some sneak peeks into the exhibitor area, I attended some of the morning keynote presentations, which focused on artificial intelligence (AI) and machine learning (ML) topics.… Read More

AI Chip Prototyping Plan

I recently had the opportunity to sit down with a chip designer for an AI start-up to talk about using FPGA prototyping as part of a complex silicon verification strategy. Like countless other chip designers for whom simulation alone simply does not provide sufficient verification coverage, this AI start-up also believed that… Read More

WEBNAR: How ASIC/SoC Rapid Prototyping Solutions Can Help You!

If you are considering an FPGA prototype for an ASIC or SoC as part of your verification strategy, which more and more chip designers today are doing to enhance verification coverage of complex designs, please take advantage of this webinar replay:

How ASIC/SoC Prototyping Solutions Can Help You!

Or to get a quick quote from S2C … Read More

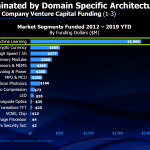

Are the 100 Most Promising AI Start-ups Prototyping?

I came across a report on the 100 most promising AI start-ups. The report claimed that CBInsights had “selected the 100 most promising AI start-ups from a pool of 3K+ companies based on several factors …” Wait, what … 3K+ companies!?!? This was a stunning reminder of the sheer magnitude of what is shaping up to be a veritable tsunami… Read More

FPGA Prototyping for AI Product Development

I recently wrote about The Implications of the Rise of AI/ML in the Cloud. In that article, I wrote about my expectation that the rapidly growing AI market will lead to the accelerated use of high-level synthesis (HLS), prototyping, and emulation. In this article, I will focus on the prototyping portion of that – specifically FPGA… Read More

The Implications of the Rise of AI/ML in the Cloud

Recently, Daniel Nenni blogged on the presentation Wally Rhines gave at #56th DAC. Daniel provided a great summary, but I want to dive into a portion of the presentation in more detail. I love Wally’s presentations, but sometimes you cannot absorb the wealth of information he provides when you initially see it. It’s… Read More

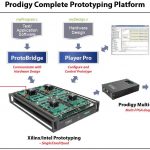

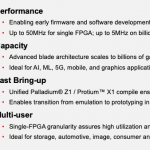

Cadence Releases Enterprise-Level FPGA Prototyping

Big prototyping hardware is essential to modern firmware and software development for pre-silicon, multi-billion gate hardware. For hardware verification it complements emulation, running fast enough for realistic testing on big software loads while still allowing fast-switch to emulation for more detailed debug where… Read More

Automotive Design and Virtual Prototyping

The entire history of EDA software tools has enabled engineers to design ICs and SoCs using virtual prototyping, so most of us in the industry are familiar with the idea of modeling and simulating something as complex as an IC before actually starting the manufacturing process. In a complex system like an automobile there are a lot… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?