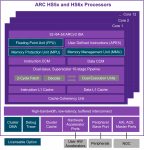

Synopsys issued a press release this morning that has some important news – Synopsys Introduces New 64-bit ARC Processor IP Delivering Up to 3x Performance Increase for High-End Embedded Applications. At first glance, one could assume this is just an announcement for some new additions to the popular ARC processor family. While… Read More

Security in I/O Interconnects

I got a chance to chat with Richard Solomon at Synopsys recently about a very real threat for all of us and what Synopsys is doing about it. No, the topic isn’t the Coronavirus, it’s one that has been around a lot longer and will continue to be a very real threat – data and interconnect security.

First, a bit about Richard. He is the technical… Read More

IP to SoC Flow Critical for ISO 26262

In thinking about automotive electronics safety standards, such as ISO 26262, it is easy to jump to the conclusion that they are in reference to systems such as autonomous driving, which are entering the marketplace. In reality, functional safety in automotive electronics plays a significant role in many well-established automotive… Read More

New ARC VPX DSP IP provides parallel processing punch

The transition to the digital age from a mostly analog world really began with the invention of the A-to-D and D-to-A converters. However scalar processors can easily be overwhelmed by the copious data produced by something as simple as an audio stream. To solve this problem and to really jumpstart the digital age, the development… Read More

Functional Safety ARC Processor IP will speed automotive system design

In the automotive space you can’t even get out of the starting gate without Functional Safety (FS). All electronic system that go into cars must have ISO 26262 certification. However, this is not something you slap on after the fact. From the ground up the requirements for ISO 26262 must be considered and the proper processes must… Read More

Synopsys and Infineon prepare for expanding AI use in automotive applications

We all know that cars are using processors for many tasks, but it is easy to fail to comprehend just how many there are in a typical modern car. Browsing through the Infineon AURIX automotive processor application guide, you can start to see just how pervasive processors are. The AURIX processors are specifically designed for automotive… Read More

Synopsys is First IP Provider with a Complete CXL Implementation Available

Synopsys just announced the availability of their IP solution supporting CXL (Compute Express Link). This new protocol is going to be an important component for several applications expected to be shipping starting in 2021. CXL is an alternate protocol that runs on the same physical layer as PCI Express (PCIe). Among other usages,… Read More

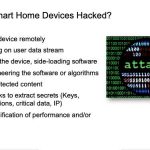

Synopsys and Synaptics Talk About Securing the Connected Home

Like many people, I have been adding automation to my home, and the number of connected devices I use has slowly but steadily increased. These include light bulbs, cameras, switches, a thermostat, a voice assistant, etc. Between them, they know when I am home or away, and have the ability to record images and sound. In addition to … Read More

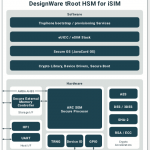

Integrated SIMs Will Unlock IoT Growth

I’m a believer that connectivity for the IoT at scale (the trillions of devices that the industry predicts) has to be cellular. This is partly based on reach, particularly outside urban areas, but is mostly based on the financial implications of that scale. Yes, you can build infrastructure for say local Wi-Fi support with backhaul… Read More

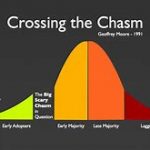

Tortuga Crosses a Chasm

I assume you know the Geoffrey Moore “crossing the chasm” concept, jumping from early stage enthusiasts trying your product because they’ll try anything new, to expanding to a mainstream and intrinsically more critical audience – a much tougher proposition. I’d argue there may be more than one of these transitions in the… Read More