The TSMC Technology Symposium recently kicked off in Santa Clara, with a series of events scheduled around the world. This event showcases the latest TSMC technology. It is also an opportunity for TSMC’s vast ecosystem to demonstrate commercial application on TSMC’s technology. There is a lot to unpack at an event like this. There… Read More

Semiconductor Intellectual Property

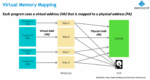

RISC-V Virtualization and the Complexity of MMUs

In the early days of RISC-V adoption, applications were microcontroller-centric with no need for virtualization support. But horizons expanded and now RISC-V is appearing in application processors, very much needing to be able to virtualize multiple apps concurrently. Take another step forward to datacenter servers running… Read More

Intel’s Foundry Transformation: Technology, Culture, and Collaboration

Intel’s historical dominance in semiconductor process technology began to erode around 2018, as competitors started delivering higher performance at smaller nodes. In response, Intel is now doubling down on innovation across two fronts: advanced process nodes such as Intel 18A and 14A, and cutting-edge packaging technologies.… Read More

Silicon Creations Presents Architectures and IP for SoC Clocking

Design & Reuse recently held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP is now the fuel for a great deal of innovation in semiconductor design. This popular event allows IP providers to highlight the latest products and services and share a vision of the future. IP consumers can easily get updates on… Read More

Emerging NVM Technologies: ReRAM Gains Visibility in 2024 Industry Survey

A recent survey of more than 120 anonymous semiconductor professionals offers a grounded view of how the industry is evaluating non-volatile memory (NVM) technologies—and where things may be heading next.

The 2024 NVM Survey, run in late 2024 and promoted through various semiconductor-related platforms and portals including… Read More

Scaling AI Infrastructure with Next-Gen Interconnects

At the recent IPSoC Conference in Silicon Valley, Aparna Tarde gave a talk on the importance of Next-Gen Interconnects to scale AI infrastructure. Aparna is a Sr. Technical Product Manager at Synopsys. A synthesis of the salient points from her talk follows.

The rapid advancement of artificial intelligence (AI) is fundamentally… Read More

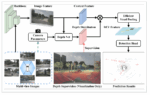

Recent AI Advances Underline Need to Futureproof Automotive AI

The world of AI algorithms continues to advance at a furious pace, and no industry is more dependent on those advances than automotive. While media and analysts continue to debate whether AI will deliver value in business applications, there is no question that it adds value to cars, in safety, some level of autonomous driving, … Read More

The Growing Importance of PVT Monitoring for Silicon Lifecycle Management

In an era defined by complex chip architectures, ever-shrinking technology nodes and very demanding applications, Silicon Lifecycle Management (SLM) has become a foundational strategy for optimizing performance, reliability, and efficiency across the lifespan of a semiconductor device. Central to effective SLM are Process,… Read More

Designing and Simulating Next Generation Data Centers and AI Factories

At NVIDIA’s recent GTC conference, a Cadence-NVIDIA joint session provided insights into how AI-powered innovation is reshaping the future of data center infrastructure. Led by Kourosh Nemati, Senior Data Center Cooling and Infrastructure Engineer from NVIDIA and Sherman Ikemoto, Sales Development Group Director from … Read More

How Cadence is Building the Physical Infrastructure of the AI Era

At the 2025 NVIDIA GTC Conference, CEO Jensen Huang delivered a sweeping keynote that painted the future of computing in bold strokes: a world powered by AI factories, built on accelerated computing, and driven by agentic, embodied AI capable of interacting with the physical world. He introduced the concept of Physical AI—intelligence… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!