In fact KitKat advocates low-power always-on functionality, and this is essential for contextual-awareness. Always-on functionality is saving battery life, which seems to be weird at first: if your phone is always-on you would expect it to consume much power… But always-on goes together with screen-off (the screen is a high… Read More

Semiconductor Intellectual Property

Can Intel Compete in the IoT?

Kevin Ashton, a British technology pioneer, is credited for the term “The Internet of Things” to describe an ecosystem where the Internet is connected to the physical world via ubiquitous sensors. Simply stated: rather than humans creating content for the internet IoT devices create the content. To be clear, this… Read More

nVidia: Virtual Platform/Emulation Hybrid

I was the VP marketing at VaST Systems Technology and then at Virtutech. Both companies sold virtual platform technology which consisted of two parts:

- an extremely fast processor emulation technology that actually worked by doing a binary translation of the target binary code (e.g. an ARM) into the native instruction set of the

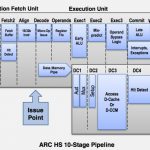

Synopsys Creates a High-performance ARC Core

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

GlobalFoundries and ARM

GlobalFoundries had several interesting things at the ARM TechCon last week. Firstly, GlobalFoundries won the best in show award in the chip design category recognizing the best-in-class technologies introduced since the last TechCon.

Earlier in the summer GlobalFoundries and ARM announced the ARM Cortex-A12 processor,… Read More

Fabless: The Transformation of the Semiconductor Industry

As I have mentioned before, Paul McLellan and I are writing a book on the history of the fabless semiconductor industry. There is a preview available HERE, it will initially be sold as an e-book on SemiWiki and put into print early next year. Working with Paul McLellan and Beth Martin on this was an amazing experience. The research,… Read More

SEMICO Impact 2013 Next Wednesday

Semico’s IMPACT 2013 IP event is next Wednesday November 6th at the DoubleTree Hilton in San Jose.

Here’s what you get if you attend. Keynotes from:

- Kurt Shuler of Arteris. Give him some hard questions about Qualcomm who have just acquired their technology and engineering team

- Chris Rowen of Tensilica, recently acquired

Using OTP Memories for High-performance Video

One of the most demanding applications where semiconductors are used is in the various applications of digital video from tablet computers, to home entertainment. iPad with a retina display is already at high-definition (HD) resolution (2048×1536) and all indications are that video is racing towards what is known as 4K… Read More

ARM and the Internet of Things

I was at ARM TechCon earlier this week, and attended Simon Segars (the CEO of ARM for the last 4 months) keynote speech that opened the second day. A theme of his speech was that just as innovation continues to happen in so-called mature industries like automobiles, the same will happen in mobile. One particular area of focus for ARM… Read More

Intel is Killing the Environment!

If I had to sum up opening day at ARM TechCon 2013 in one word it would be “crowded”. More than twice as many people attended as last year with 6,500 preregistered. The opening keynote was “The New Style of IT” pimping the HP Moonshot systems, but it could have just as easily been called “Why Intel Stock is Dead Money”,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?