If you have a phone, you probably know it has a SIM card, for most of us the anchor that ties us into a 2/3-year plan with one network provider, unless you have an unlocked phone. Even then, you have to mess around swapping SIM cards if you travel overseas. Wouldn’t it be nice if the SIM was embedded and could be switched though an app or an… Read More

Semiconductor Intellectual Property

Data Security – Why It Might Matter to Design and EDA

According to the Economist, “The world’s most valuable resource is no longer oil, but data”. Is this the case?Data is the by-product ofmany aspects of recent technology dynamics and is becoming the currency of today’s digital economy. All categories in Gartner’s Top10 Strategic Technology Trends for 2018 (Figure… Read More

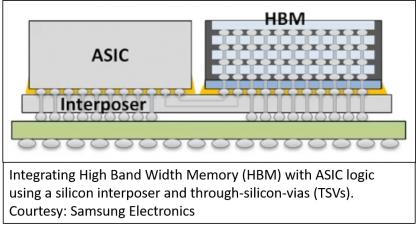

High Performance Ecosystem for 14nm-FinFET ASICs with 2.5D Integrated HBM2 Memory

High Bandwidth Memory (HBM) systems have been successfully used for some time now in the network switching and high-performance computing (HPC) spaces. Now, adding fuel to the HBM fire, there is another market that shares similar system requirements as HPC and that is Artificial Intelligence (AI), especially AI systems doing… Read More

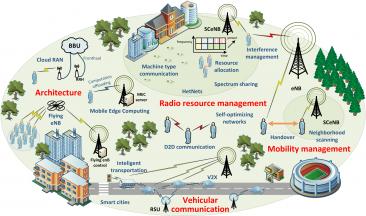

Increased Processing Power Moves to Edge

Recently there has been a lot of buzz about 5G networks. Aside from the talk about it possibly being nationalized, 5G will be a lot different than its predecessors. Rather than a single data link in a predetermined band, 5G will consist of a web of connections all working together to support existing types of data traffic and many new… Read More

CES: An Exhibitor’s Takeaway

There are few tech promises these days as prominent as those surrounding driverless cars (trucks, buses, …). But thanks to always-on media amplifiers, it’s not always easy to separate potential from reality. I recently talked to Kurt Shuler, VP Marketing at Arteris, who shared his view after returning from this year’s CES. Kurt… Read More

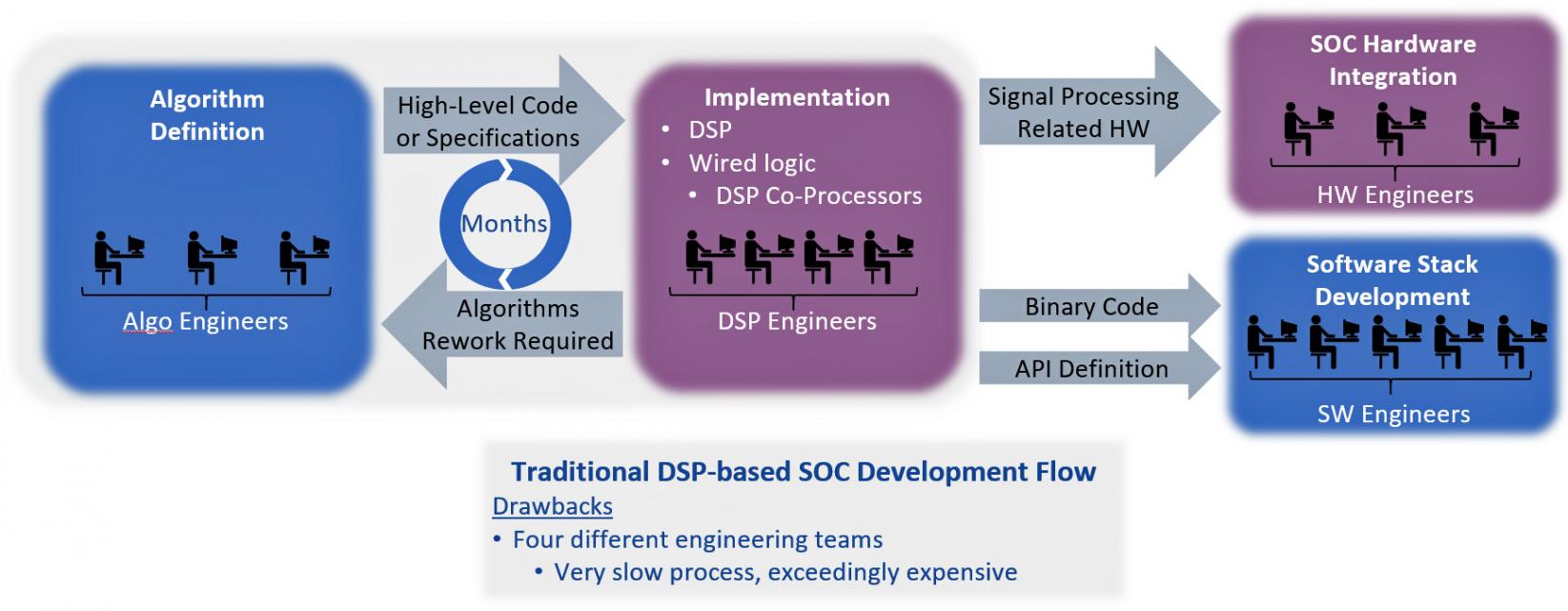

DSP SoC a la Française

I enjoyed reading Eric Esteve’s article “ French Tech at CES, 2nd country after USA with 274 Start-Up at Eureka Park!” It brought back happy memories of my time at EVE until Synopsys purchased it in 2012.Here is another intriguing story by a French startup named VSORA and founded by Khaled Maalej with a team of scientists and engineers.… Read More

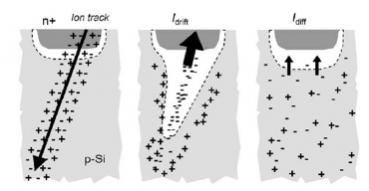

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

Wanted by January 30th: Paper for DAC IP Track 2018!

DAC 2018 will take place in San Francisco in June (24 to 28) and you have a fantastic opportunity to present a paper in the IP track! In fact, the deadline has been extended to January 30[SUP]th[/SUP] to submit your proposal.

Let’s make it clear: you are not expected to send the completed paper by this date, just the following:

- The title

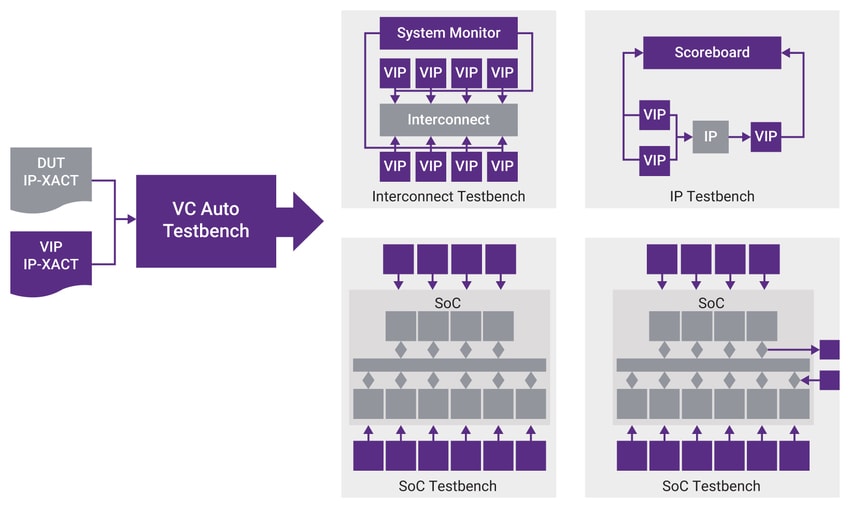

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

Context is Everything – especially for autonomous vehicle IP

GM has just announced that it will introduce a car with no steering wheel or pedals in 2019. According to their statement, they have already planned four phases of their autonomous driving system, and they will plan many more. However, before we jump into this latest car and not grab the wheel for a spin, it is reasonable to ask about… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era