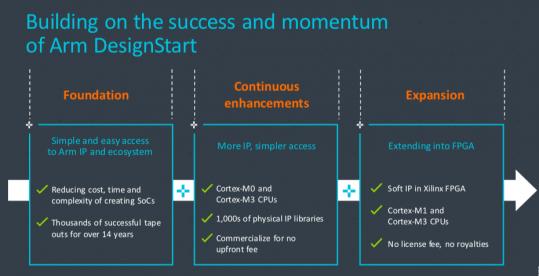

Many of us dream about the wonderful widget we could build that would revolutionize our homes, parking, health, gaming, factories or whatever domain gets our creative juices surging, but how many of us take it the next step? Even when you’re ready to live on your savings, prototypes can be expensive and royalties add to the pain. … Read More

Semiconductor Intellectual Property

Synopsys Seeds Significant SIM Segue

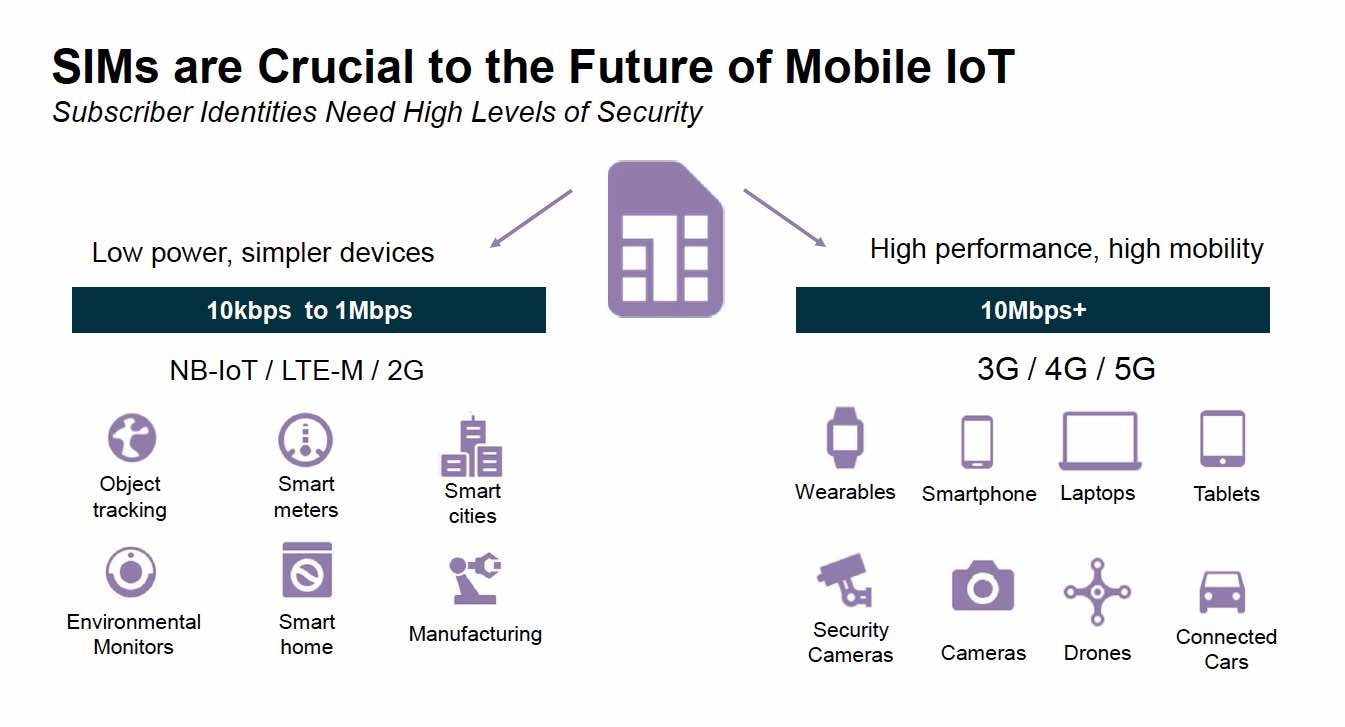

It turns out that consumers are not alone in their love-hate relationship with SIM cards. SIM cards save us from increasingly widespread cellphone cloning. However, if your experience is anything like mine, it seemed that with every new phone, a new SIM card format was needed. Furthermore, people travelling overseas who wanted… Read More

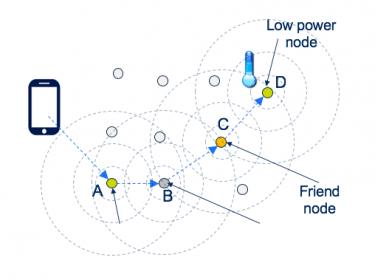

Mesh Networks, Redux

It isn’t hard to understand the advantage of mesh networking (in wireless networks). Unlike star/tree configurations in which end-points connect to a nearby hub (such as phones connecting to a conventional wireless access point), in a mesh nodes can connect to nearest neighbors, which can connect to their nearest neighbors… Read More

Crossfire Baseline Checks for Clean IP at TSMC OIP

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More

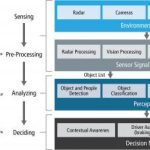

Highly Modular, AI Specialized, DNA 100 IP Core Target IoT to ADAS

The Cadence Tensilica DNA100 DSP IP core is not a one-size-fits-all device. But it’s highly modular in order to support AI processing at the edge, delivering from 0.5 TMAC for on-device IoT up to 10s or 100 TMACs to support autonomous vehicle (ADAS). If you remember the first talks about IoT and Cloud, a couple of years ago, the IoT … Read More

Neural Network Efficiency with Embedded FPGA’s

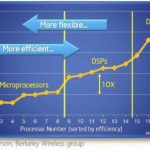

The traditional metrics for evaluating IP are performance, power, and area, commonly abbreviated as PPA. Viewed independently, PPA measures can be difficult to assess. As an example, design constraints that are purely based on performance, without concern for the associated power dissipation and circuit area, are increasingly… Read More

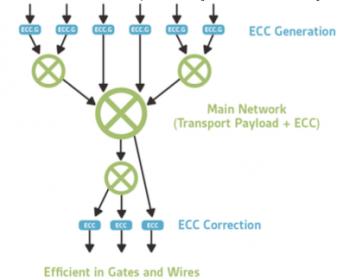

Supporting ASIL-D Through Your Network on Chip

The ISO 26262 standard defines four Automotive Safety Integrity Levels (ASILs), from A to D, technically measures of risk rather than safety mechanisms, of which ASIL-D is the highest. ASIL-D represents a failure potentially causing severe or fatal injury in a reasonably common situation over which the driver has little control.… Read More

Semiconductor IP Reality Check

A robust, proven library of IP is a critical enabler for the entire semiconductor ecosystem. Without it, ASIC design is pretty much impossible, given time-to-market pressures. Said another way, designing IP for your next chip simply doesn’t fit the schedule – most teams have barely enough time to integrate and validate pre-existing… Read More

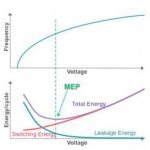

Integrated Power Management IP to Decrease Power and Cost

This blog is the synthesis of a white paper “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, which can be found on Dolphin Integration web site.

The power consumption generated by complex chips was not a real issue when the system could be simply plugged in the wall to … Read More

DesignWare IP as AI Building Blocks

AI is disruptive and transformative to many status quos. Its manifestation can be increasingly seen in many business transactions and various aspects of our lives. While machine learning (ML) and deep learning (DL) have acted as its catalysts on the software side, GPU and now ML/DL accelerators are spawning across the hardware… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era