Another content-rich kickoff covering a lot of bases under three main themes: the new Millennium AI supercomputer release, a moonshot towards full autonomy in chip design exploiting agentic AI, and a growing emphasis on digital twins. Cadence President and CEO Anirudh Devgan touched on what is new today, and also market directions… Read More

Designing and Simulating Next Generation Data Centers and AI Factories

At NVIDIA’s recent GTC conference, a Cadence-NVIDIA joint session provided insights into how AI-powered innovation is reshaping the future of data center infrastructure. Led by Kourosh Nemati, Senior Data Center Cooling and Infrastructure Engineer from NVIDIA and Sherman Ikemoto, Sales Development Group Director from … Read More

How Cadence is Building the Physical Infrastructure of the AI Era

At the 2025 NVIDIA GTC Conference, CEO Jensen Huang delivered a sweeping keynote that painted the future of computing in bold strokes: a world powered by AI factories, built on accelerated computing, and driven by agentic, embodied AI capable of interacting with the physical world. He introduced the concept of Physical AI—intelligence… Read More

Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

The semiconductor industry is facing a paradigm shift. Traditional scaling, once driven by Moore’s Law, is slowing down. For years, moving to smaller process nodes led to lower transistor costs and better performance. However, scaling from node to node now offers fewer benefits as wafer costs rise much more than the historical… Read More

Accelerating Automotive SoC Design with Chiplets

The automotive industry is evolving rapidly with the increasing demand for intelligent, connected, and autonomous vehicles. Central to this transformation are System-on-Chip (SoC) designs, which integrate multiple processing units into a single chip for managing everything from safety systems to in-car entertainment.… Read More

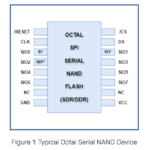

Overcoming Verification Challenges of SPI NAND Flash Octal DDR

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

The Impact of UCIe on Chiplet Design: Lowering Barriers and Driving Innovation

The semiconductor industry is experiencing a significant transformation with the advent of chiplet design, a modular approach that breaks down complex chips into smaller, functional blocks called chiplets. A chiplet-based design approach offers numerous advantages, such as improved performance, reduced development … Read More

Empowering AI, Hyperscale and Data Center Connectivity with PAM4 SerDes Technology

The rapid expansion of data-intensive applications, such as artificial intelligence (AI), high-performance computing (HPC), and 5G, necessitates connectivity solutions capable of handling massive amounts of data with high efficiency and reliability. The advent of 224G/112G Serializer/Deserializer (SerDes) technology,… Read More

Cadence® Janus™ Network-on-Chip (NoC)

A Network-on-Chip (NoC) IP addresses the challenges of interconnect complexity in SoCs by significantly reducing wiring congestion and providing a scalable architecture. It allows for efficient communication among numerous initiators and targets with minimal latency and high speed. A NoC facilitates design changes, enabling… Read More

Automotive Electronics Trends are Shaping System Design Constraints

Something is brewing in automotive electronics. Within a one-month window most of the product announcements and pitches to which I am being invited are on automotive topics. Automotive markets have long been one of the primary targets for suppliers to system designers, but this level of alignment in announcements seems more … Read More