Timing closure is the perennial issue in digital IC design. While the specific problem that has needed to be solved to achieve timing closure over the decades has continuously changed, it has always been a looming problem. And the timing closure problem has gotten more severe with 16/14nm FinFET SoCs due to greater distances between… Read More

IP development strategy and hockey

One of the greatest hockey players of all time, Wayne Gretzky, provided a quote that has also been applied to the business world — “I skate to where the puck will be, not to where it has been.” It strikes me that this philosophy directly applies to IP development, as well. Engineering firms providing IP must anticipate… Read More

It’s All About the Models

The world-renowned statistician, Professor George Box, said, “Essentially, all models are wrong, but some are useful.” — that quote was the theme for one of the technical talks at the recent MOS-AK Workshop, held at UC-Berkeley. … Read More

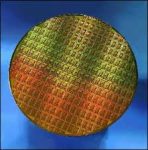

Making the Move from 28nm to FinFET!

If you click FinFET in the SemiWiki.com Latest News: navigation bar at the top of this page you will get a list of 86 blogs that have been viewed more than 600,000 times. If you go to the last blogs on the list, meaning the first blogs to be published, you will see a three part series, “Introduction to FinFET Technology” written by Tom Dillinger… Read More

Analog Bits and TSMC!

As a long time semiconductor IP professional I can tell you for a fact that it is one of the most challenging segments of semiconductor design. Given the growing criticality of semiconductor IP, the challenges of being a leading edge IP provider are increasing and may be at a breaking point. The question now is: What does it take to … Read More

CEO Interview: Albert Li of Platform DA

Platform Design Automation, Inc (PDA). recently closed a US$6 million pre Series A investment round, and the company has shifted its focus from providing SPICE modeling related software and services to forming a complete AI-driven ecosystem from probing to simulation. Albert Li was the GM of Accelicon, a leading EDA tool and … Read More

ATPG, Automotive and 7nm FinFET

The state of Texas hosted two or our industry’s big technical conferences and trade shows this year: DAC and ITC (International Test Conference). IC designers know about DAC in Austin, and test engineers know about ITC in Dallas. I travelled to Austin to cover DAC this past summer, and I was able to connect with Robert Ruiz … Read More

5 of the Top 20 Semiconductor Suppliers to Show Double-Digit Gains in 2016!

Semiconductor Market Researcher IC Insights released an update to the 2016 semiconductor sales forecast which is interesting on many different levels. It really has been an exciting year for the semiconductor industry, absolutely. Two of the stars of this year’s report happen to be two of my favorite fabless companies, Nvidia… Read More

Always-On IoT – FDSOI’s Always Better? What About Wafers? (Questions from Shanghai)

Mahesh Tirupattur, EVP at low-power SERDES pioneer Analog Bits lead off the panel discussion at the recent FD-SOI Forum in Shanghai with the assertion that for anything “always on” in IoT, FD-SOI’s always better. They had a great experience porting their SERDES IP to 28nm FD-SOI (which they detailed last spring – see the ppt here… Read More

Webinar Offers View into TSMC IP Design Methodology

Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center