This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. The presentation covered here from Synopsys focuses on the… Read More

WEBINAR: UVM RISC-V and DV

Oh, our semiconductor industry just loves acronyms, and the title of my blog packs three of the most popular acronyms together at once. I attended a webinar hosted by Aldec last week on this topic, “UVM Simulation-based environment for Ibex RISC-V CPU core with Google RISC-V DV“. Verification engineers have been … Read More

WEBINAR: Design Adaptive eFPGA IP

Since the start of PROMS, PLDs and FPGAs we have learned the importance of programmability in modern semiconductor design. Today we have eFPGAs for “design adaptive” embedded programmability and that is what this webinar is all about.

Several key points are discussed starting with the Law of Accelerating Returns as it applies… Read More

GLOBALFOUNDRIES Goes Virtual with 2020 Global Technology Conference Series!

GlobalFoundries is one of the more interesting semiconductor stories of this decade. They started as a spinout of the AMD fabs then acquired Chartered Semiconductor Manufacturing in 2009 and the IBM Microelectronics business in 2014.

Now that events are virtual it is a great time for my fellow semiconductor professionals to

VLSI Symposium 2020 – Imec Monolithic CFET

The 2020 VLSI Technology Symposium was held as a virtual conference from June 14th through June 19th. At the symposium Imec gave an interesting paper on Monolithic CFET and I had a chance to interview one of the authors, Hiroaki Arimura.

It is well known in the industry that FinFETs (FF) are reaching the end of their scaling life. Samsung… Read More

Online Verification Meet-up With Intel and Arm!

Veriest is headquartered in Israel with engineering sites in Serbia & Hungary. The team has accumulated a wealth of experience through involvement in projects in the forefront of semiconductor technology.

Veriest maintains unrivaled quality standards in terms of both service and knowledge. With the ability to take on … Read More

Analog Bits at TSMC OIP – A Complete On-Die Clock Subsystem for PCIe Gen 5

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. The talk covered here focuses on a complete on-die clock … Read More

Highlights of the TSMC Technology Symposium – Part 3

Recently, TSMC held their 26th annual Technology Symposium, which was conducted virtually for the first time. This article is the last of three that attempts to summarize the highlights of the presentations. This article focuses on the technology design enablement roadmap, as described by Cliff Hou, SVP, R&D.

Key Takeaways… Read More

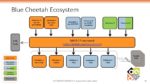

Blue Cheetah Technology Catalyzes Chiplet Ecosystem

There are many reasons today for dividing up large monolithic SoCs into chiplets that are connected together inside a single package. Let’s look at just some of these reasons. Many SoCs share a common processing core with application specific interfaces and specialized processing engines. Using chiplets would mean that it is… Read More

Dolphin Design – Delivering High-Performance Audio Processing with TSMC’s 22ULL Process

TSMC held their very popular Open Innovation Platform event (OIP) on August 25. The event was virtual of course and was packed with great presentations from TSMC’s vast ecosystem. One very interesting and relevant presentation was from Dolphin Design, discussing the delivery of high-performance audio processing using TSMC’s… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era