Machine learning-based applications have become prevalent across consumer, medical, and automotive markets. Still, the underlying architecture(s) and implementations are evolving rapidly, to best fit the throughput, latency, and power efficiency requirements of an ever increasing application space. Although ML is … Read More

Know what 5G is? You’re probably wrong

If you think the transition to 5G will be anything like the transitions before it to 3G or 4G, you are in for a big surprise. Not only will the transition take longer than either of the previous transitions, its ramifications will spread far beyond cell phones and into other areas such as automobiles, AI, healthcare, and commerce. … Read More

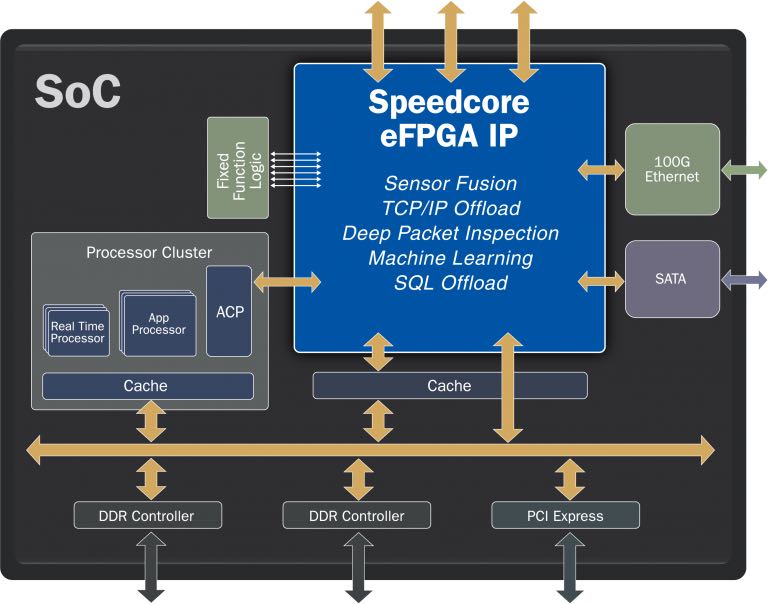

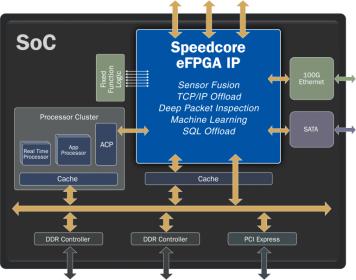

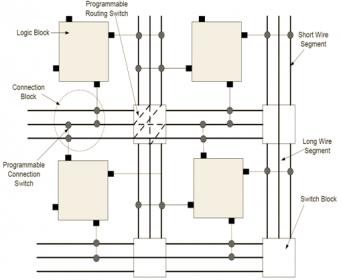

When Why and How Should You Use Embedded FPGA Technology

If integrating an embedded FPGA (eFPGA) into your ASIC or SoC design strikes you as odd, it shouldn’t. ICs have been absorbing almost every component on a circuit board for decades, starting with transistors, resistors, and capacitors — then progressing to gates, ALUs, microprocessors, and memories. FPGAs are simply one more… Read More

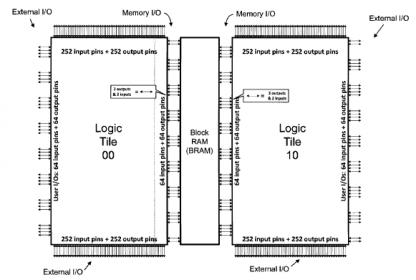

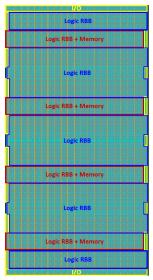

Block RAM integration for an Embedded FPGA

The upcoming Design Automation Conference in San Francisco includes a very interesting session –“Has the Time for Embedded FPGA Come at Last?” Periodically, I’ve been having coffee with the team at Flex Logix, to get their perspective on this very question – specifically, to learn about the key features that customers are seeking… Read More

Hard IP for an embedded FPGA

As Moore’s Law enables increased integration, the diversity of functionality in SoC designs has grown. Design teams are seeking to utilize outside technical expertise in key functional areas, and to accelerate their productivity by re-using existing designs that others have developed. The Intellectual Property (IP) industry… Read More

Achronix Momentum Building with Revenue Growth, Product/Staff Expansion, New HQ

5G Wireless, Network Acceleration, Data centers, Machine Learning, Compression, Encryption fueling the Growth

Building on its increasing momentum, Achronix Semiconductor Corporation held a ribbon-cutting ceremony on Tuesday, April 25, with the presence of Santa Clara’s Mayor Lisa Gillmor, customers, and partners, employees… Read More

Configurability for Embedded FPGA Hard IP

IP providers need to evaluate several complex engineering problems when addressing customer requirements – perhaps the most intricate challenge is the degree of IP configurabilityavailable to satisfy unique customer applications. … Read More

New Architectures for Automotive Intelligence

My first car was a used 1971 Volvo 142 and probably did not contain more than a handful of transistors. I used to joke that it could easily survive the EMP from a nuclear explosion. Now, of course, cars contain dozens or more processors, DSP’s and other chips containing millions of transistors. It’s widely expected that the number … Read More

Processing Power Driving Practicality of Machine Learning

Despite their recent rise to prominence, the fundamentals of AI, specifically neural networks and deep learning, were established as far back as the late 50’s and early 60’s. The first neural network, the Perceptron, had a single layer and was good certain types of recognition. However, the Perceptron was unable to learn how to… Read More

The hierarchical architecture of an embedded FPGA

The most powerful approach to managing the complexity of current SoC hardware is the identification of hierarchical instances with which to assemble the design. The development of the hierarchical design representation requires judicious assessment of the component definitions. The goals for clock distribution, power … Read More

Things From Intel 10K That Make You Go …. Hmmmm