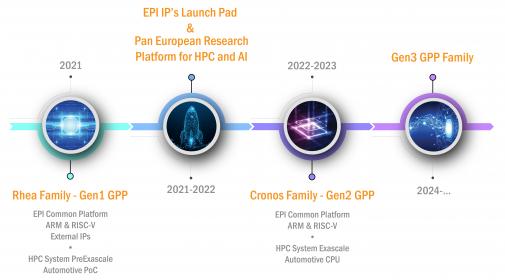

During 2018, Menta looked quiet if you consider communication as the main indicator of activity. In fact, the eFPGA vendor was hyper-active in developing future business and reports two main design-win. The first is with the European Processor Initiative (EPI) and Menta has announced in December 2018 that it has been selected… Read More

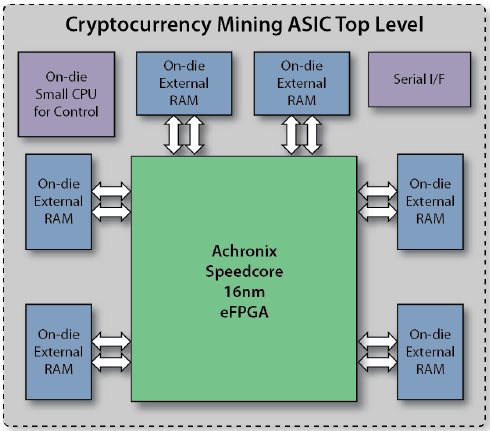

Newer cryptocurrencies highlight need for agile mining strategies

Cryptocurrencies represent a radical departure from traditional forms of money. Currencies like Bitcoin, Etherium and Monero offer many unique advantages over traditional currencies, and are changing how money is created and used. Bitcoin, the pioneer of cryptocurrencies, relies on pure computational power for so-called… Read More

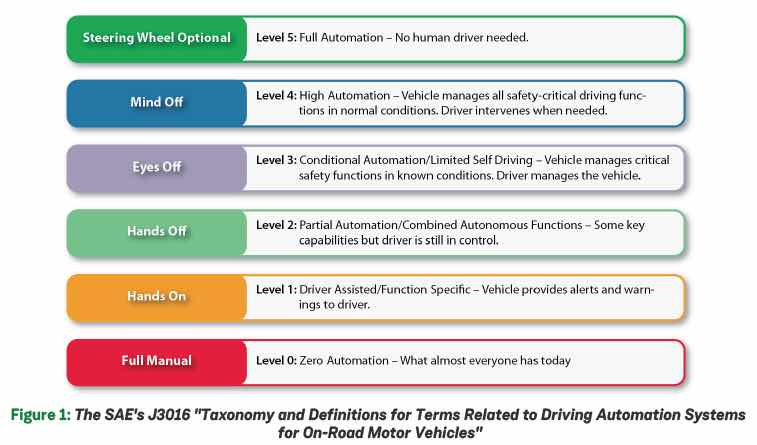

Building Better ADAS SOCs

Ever since we replaced horses in our personal transportation system, folks have been pining for cars that offer some relief from the constant need for supervision, control and management. Indeed, despite their obvious downsides, horses could be counted on to help with steering and obstacle avoidance. There are even cases when… Read More

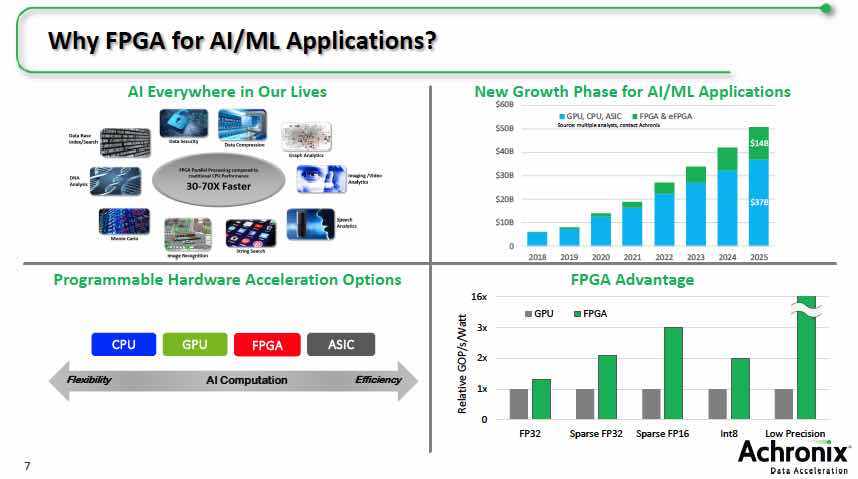

AI at the Edge

Frequent Semiwiki readers are well aware of the industry momentum behind machine learning applications. New opportunities are emerging at a rapid pace. High-level programming language semantics and compilers to capture and simulate neural network models have been developed to enhance developer productivity (link). Researchers… Read More

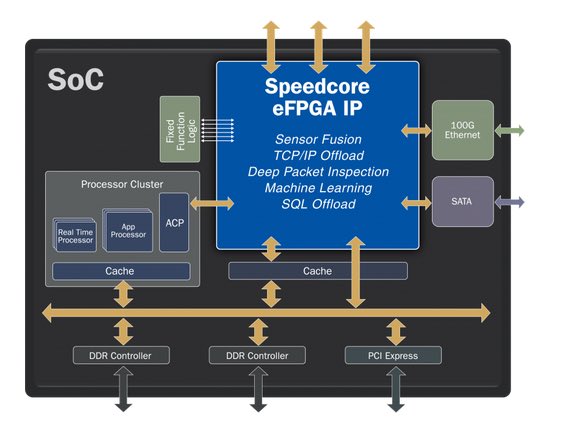

Embeddable FPGA Fabric on TSMC 7nm

With their current line-up of embeddable and discrete FPGA products, Achronix has made a big impact on their markets. They started with their Speedster FPGA standard products, and then essentially created a brand-new market for embeddable FPGA IP cores. They have just announced a new generation of their Speedcore embeddable… Read More

Achronix Assists Academics

In every semiconductor related field, innovation is the name of the game. Academic, non-profit and government research has been a consistent source of innovation. Look back at the US space program, basic science research and even military programs to see where much of the foundation of our current technological age came from.… Read More

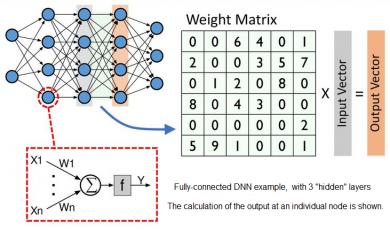

Architecture for Machine Learning Applications at the Edge

Machine learning applications in data centers (or “the cloud”) have pervasively changed our environment. Advances in speech recognition and natural language understanding have enabled personal assistants to augment our daily lifestyle. Image classification and object recognition techniques enrich our social media experience,… Read More

Avionics and Embedded FPGA IP

The design of electronic systems for aerospace applications shares many of the same constraints as apply to consumer products – e.g., cost (including NRE), power dissipation, size, time-to-market. Both market segments are driven to leverage the integration benefits of process scaling. … Read More

Neural Network Efficiency with Embedded FPGA’s

The traditional metrics for evaluating IP are performance, power, and area, commonly abbreviated as PPA. Viewed independently, PPA measures can be difficult to assess. As an example, design constraints that are purely based on performance, without concern for the associated power dissipation and circuit area, are increasingly… Read More

An FPGA Industry Veteran’s View of Future

There are tectonic changes happening in the world of FPGAs. A lot has changed since their introduction in the 80’s. Back then they were mostly used to implement state machines or glue logic. Subsequently they grew more complex with the addition of high speed IOs, eRAM, DSPs, other processors and other IP. More recently though FPGAs… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint