One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

How Well is HSPICE Tracking Current Design Trends?

For about 5 years now Synopsys has held an HSPICE SIG event in conjunction with DesignCon. It features a small vendor faire with companies that partner with Synopsys on HSPICE flows. They also have a dinner with industry/customer speakers and provide an update on HSPICE development. Lastly there is a Q&A where customers get… Read More

What’s New with Static Timing Analysis

When I hear the phrase Static Timing Analysis (STA) the first EDA tool that comes to mind is PrimeTimefrom Synopsys, and this type of tool is essential to reaching timing closure for digital designs by identifying paths that are limiting chip performance. Sunil Walia, PrimeTime ADV marketing lead spoke with me by phone on Thursday… Read More

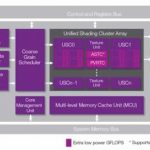

How Imagination tested the PowerVR Series6XT

We have been hearing for some time about the Synopsys HAPS-70 and how they have co-created the hardware and software architecture for FPGA-based prototyping with their customers. Now, we see details published by Synopsys on how they collaborated with Imagination on the design of the PowerVR Series6XT GPU.

The first thing to come… Read More

Prototyping Kits to Accelerate IP Development & Integration into SoCs

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More

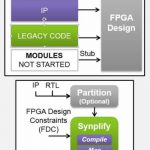

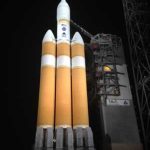

Synthesizing rad-tolerant RTL for FPGAs

The maiden voyage of NASA’s Orion spacecraft brought a raft of articles about how the flight computer inside is “no smarter than your phone,” running on wheezing IBM PowerPC 750FX processors. NASA’s deputy manager for Orion avionics, Matt Lemke, admits the configuration is already obsolete – at least in commercial terms. … Read More

Synopsys Q4 Earnings

Synopsys announced their earnings a couple of days ago. This is actually also the end of their fiscal year. They had quarterly earnings of $539M meaning that they did just over $2B for the year. Their guidance for fiscal 2015 is revenue between $2.185B to $2.225B. They said that about 80% of that revenue is already in backlog.

But it… Read More

Design Rule Checking (DRC) Meets New Challenges

The traditional batch-oriented DRC process run as a final check to ensure compliance with foundry yield goals is quickly moving toward a concurrent DRC process performed early and often throughout design, especially at the 28 nm and smaller process nodes. What are the technology factors causing this change?

- Increasing number

Using HAPS-DX for system-level deep trace debug

Debugging an ASIC design in an FPGA-based prototyping system can be a lot like disciplining a puppy. If you happen to be there at the exact moment the transgression occurs and understand what led up to that moment, administering an effective correction might be possible.

Catching RTL in the act requires the right tools. Faults in… Read More

How many 28nm FDSOI SoC Design Starts in 2015? In 2020?

I would like to further discuss this graphic (presented during IP-SoC 2014 by John Koeter, VP of Marketing IP and prototyping, Synopsys) and focus on Active Design and Tapeouts at 28nm. In fact the very first activity appeared in Q1 2007, but it was only during 2010 that 28nm become popular, after the first Tapeouts coming in Q1 and… Read More