You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 789

[filter] => raw

[cat_ID] => 14

[category_count] => 789

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 789

[filter] => raw

[cat_ID] => 14

[category_count] => 789

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

More than 500 designers (562) have responded to a survey made in 2015 by Synopsys. Answering to the question “What is the fastest clock speed of your design?” 56% have mentioned a clock higher than 500 MHz (and still 40% higher than 1 GHz). If you compare with the results obtained 10 years ago, the largest proportion of answers was for… Read More

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

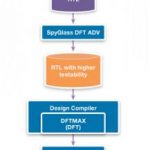

Fed up with ECOing your way out of test problems? You might want to register for this webinar.When you’re building monster SoC FPGAs, you have all the same problems you have with any other SoC. That includes getting to very high test coverage as quickly as you can with a design targeted to the most advanced processes. We’re not just … Read More

At SemiWiki we’ve been blogging for several years now on the semiconductor design challenges of FinFET technology and how it requires new software approaches to help chip designers answer fundamental questions about timing, power, area and design closure. When you mention the phrase Static Timing Analysis (STA) probably… Read More

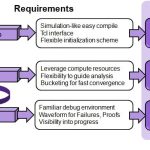

The prototype is obviously the end goal of FPGA-based prototyping, however success of the journey relies on how quickly defects can be found and rectified. Winning in the debug phase involves a combination of methodology, capability, and planning. Synopsys recently aired a webinar on their HAPS environment and its debug ecosystem.… Read More

Custom Layout Productivity Gets a Boostby Tom Dillinger on 04-11-2016 at 7:00 amCategories: EDA, Synopsys

In the 1970’s, when Moore’s Law was still in its infancy, Bill Lattin from Intel published a landmark paper [1]. In it he identified the need for new design tools and methods to improve layout productivity, which he defined as the drawn and verified number of transistors per day per layout designer. He said existing … Read More

The intricacies of analog IP circuit design have always required special consideration during physical layout. The need for optimum device and/or cell matching on critical circuit topologies necessitates unique layout styles. The complex lithographic design rules of current FinFET process nodes impose additional restrictions… Read More

We might wish that all our design automation needs could be handled by pre-packaged vendor tool features available at the push of a button, but that never was and never will be the case. In the language of crass commercialism, there may be no broad market for those features, even though you consider that analysis absolutely essential.… Read More

Synopsys hosted a lunch session on Thursday of DVCon. Michael Sanie of Synopsys opened the session, with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo… Read More