The increasing demands for massive amounts of data are driving high-performance computing (HPC) to advance the pace in the High-speed Ethernet world. This in turn, is increasing the levels of complexity when designing networking SoCs like switches, retimers, and pluggable modules. This growth is accelerating the need for … Read More

Takeaways from SNUG 2023

Synopsys pulled out all the stops for this event. I attended the first full day, tightly scripted from Aart’s keynote kick off to 1×1 interviews with Synopsys executives to a fireside chat between Sassine Ghazi (President and COO) and Rob Aitken (ex-Fellow at Arm, now Distinguished Architect at Synopsys). That’s a lot of … Read More

Full-Stack, AI-driven EDA Suite for Chipmakers

Semiconductor technology is among the most complex of technologies and the semiconductor industry is among the most demanding of industries. Yet the ecosystem has delivered incredible advances over the last six decades from which the world has benefitted tremendously. Yes, of course, the markets want that break-neck speed… Read More

Power Delivery Network Analysis in DRAM Design

My IC design career started out with DRAM design back in 1978, so I’ve kept an eye on the developments in this area of memory design to note the design challenges, process updates and innovations along the way. Synopsys hosted a memory technology symposium in November 2022, and I had a chance to watch a presentation from SK hynix… Read More

Intel Keynote on Formal a Mind-Stretcher

Synopsys has posted on the SolvNet site a fascinating talk given by Dr. Theo Drane of Intel Graphics. The topic is datapath equivalency checking. Might sound like just another Synopsys VC Formal DPV endorsement but you should watch it anyway. This is a mind-expanding discussion on the uses of and considerations in formal which … Read More

Multi-Die Systems Key to Next Wave of Systems Innovations

These days, the term chiplets is referenced everywhere you look, in anything you read and in whatever you hear. Rightly so because the chiplets or die integration wave is taking off. Generally speaking, the tipping point that kicked off the move happened around the 16nm process technology when large monolithic SoCs started facing… Read More

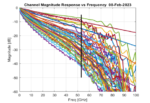

PCIe 6.0: Challenges of Achieving 64GT/s with PAM4 in Lossy, HVM Channels

As the premier high-speed communications and system design conference, DesignCon 2023 offered deep insights from various experts on a number of technical topics. In the area of high-speed communications, PCIe has a played a crucial role over the years in supporting increasingly higher communications speed with every new revision.… Read More

Synopsys Design Space Optimization Hits a Milestone

I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

Podcast EP141: The Role of Synopsys High-Speed SerDes for Future Ethernet Applications

Dan is joined by Priyank Shukla, Staff Product Manager for the Synopsys High Speed SerDes IP portfolio. He has broad experience in analog, mixed-signal design with strong focus on high performance compute, mobile and automotive SoCs and he has a US patent on low power RTC design.

Dan explores the use of high-speed SerDes with Priyank.… Read More

Webinar: Achieving Consistent RTL Power Accuracy

A comprehensive report from the US Department of Energy (DOE), “Semiconductor Supply Chain Deep Dive Assessment” (February 2022) calls for a 1000X energy efficiency improvement that is required to maintain future compute requirement needs given a finite amount of world energy production. Energy efficiency is at the top of … Read More