Looking at the Press Release (PR) flow, it was interesting to see how TSMC has solved a communication dilemma. At first, let’s precise that #1 Silicon foundry has to work with each of the big three EDA companies. As a foundry, you don’t want to lose any customer, and then you support every major design flow. Choosing another strategy… Read More

Multi-Voltage IC Design Flow

My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More

High Frequency Analysis of IC Layouts

IC designers of passive devices often use empirical approaches to perform High Frequency Analysis (HFA), however there is at least one new approach being offered by Mentor Graphics using a tool flow of:

- Device detection and extraction with Calibre LVS and Calibre PERC

- Interconnect RLC extraction with Calibre xRC, Calibre xACT-3D

Mentor Graphics Update at TSMC 2012 OIP

What

In just 20 days you can get an update on four Mentor Graphics tools as used in the TSMC Open Innovation Platform (OIP). Many EDA and IP companies will be presenting along with Mentor, so it should be informative for fabless design companies in Silicon Valley doing business with TSMC.

… Read More

Automating Complex Circuit Checking Tasks

By Hend Wagieh, Mentor Graphics

At advanced IC technology nodes, circuit designers are now encountering problems such as reduced voltage supply headroom, increased wiring parasitic resistance (Rp) and capacitance (Cp), more restrictive electromigration (EM) rules, latch-up, and electrostatic discharge (ESD) damage,… Read More

Built to last: LTSI, Yocto, and embedded Linux

The open source types say it all the time: open is better when it comes to operating systems. If you’re building something like a server or a phone, with either a flexible configuration or a limited lifetime, an open source operating system like Linux can put a project way ahead.

Linux has always started with a kernel distribution,… Read More

Wiring Harness Design

In 2003 Mentor acquired a company doing wiring harness design. Being a semiconductor guy this wasn’t an area I’d had much to do with. But more than most semiconductor people I expect.

But back when I was an undergraduate, I had worked as a programmer for a subsidiary of Philips called Unicam that made a huge range of spectrometers… Read More

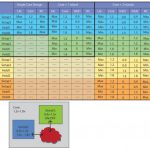

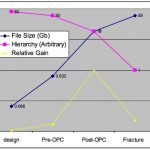

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

A Brief History of Mentor Graphics

In 1981, Pac-Man was sweeping the nation, the first space shuttle launched, and a small group of engineers in Oregon started not only a new company (Mentor Graphics), but an entirely new industry, electronic design automation (EDA).

Mentor founders Tom Bruggere, Gerry Langeler, and Dave Moffenbeier left Tektronix with a great… Read More

While you’re reading the SoC manual

There was a day, not too long ago, when a software developer could be intimate with a processor through understanding its register set. Before coding, developers would reach for a manual, digging through pages and pages of 1s and 0s with defined functions to find how to gain control over the processor and its capability. One bit set… Read More