A few months ago, I wrote about Corigine and their MimicPro FPGA prototyping system and MimicTurbo GT card solutions. That article went into the various features and benefits of the two solutions, with the requirements for next-generation prototyping solutions as the backdrop. You can access that article here. At 250+ employees,… Read More

Electronic Design Automation

WEBINAR: Challenges in analyzing High Performance clocks at 7nm and below process nodes

Proper clock functionality and performance are essential for SoC operation. Static timing analysis (STA) tools have served well for verifying clocks, yet with new advanced process nodes, lower operating voltages, higher clock speeds and higher reliability requirements, STA tools alone can’t perform the kinds of analysis… Read More

Designing Ultra-Low-Power, Always On IP

It’s popular to use DSP chips for vision processing in diverse applications like ADAS, security cameras and AR. Tensilica has been designing DSP chips and IP since 1997, and their technology was successful enough that Cadence acquired Tensilica back in 2013. At the IP-SoC Silicon Valley 2022 event in April I had the pleasure… Read More

Efficient Memory BIST Implementation

Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage… Read More

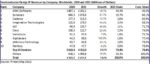

Design IP Sales Grew 19.4% in 2021, confirm 2016-2021 CAGR of 9.8%

Design IP Sales reached $5.45B in 2021, or 19.4% YoY after 16% in 2020, on-sync with semiconductor growth of 26.2% in 2021 according to WSTS. IPnest has released the “Design IP Report” in May 2022, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O,… Read More

Tensilica Edge Advances at Linley

The Linley spring conference this year had a significant focus on AI at the edge, with all that implies. Low power/energy is a key consideration, though increasing performance demands for some applications are making this more challenging. David Bell (Product Marketing at Tensilica, Cadence) presented the Tensilica NNE110… Read More

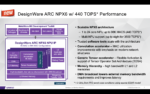

Bigger, Faster and Better AI: Synopsys NPUs

AI-based applications are fast advancing with evolving neural network (NN) models, pushing aggressive performance envelopes. Just a few years ago, performance requirements of NN driven applications were at 1 TOPS and less. Current and future applications in the areas of augmented reality (AR), surveillance, high-end smartphones,… Read More

Future.HPC is Coming!

According to the experts, the semiconductor industry is poised for a decade of growth and is projected to become a trillion dollar industry by 2030. In 2021 the semiconductor industry finally hit $600B so $1T by 2030 seems like a big ask, but not really if you look at the indicators inside the semiconductor ecosystem. Foundries, … Read More

Freemium Business Model Applied to Analog IC Layout Automation

Freemium is the two words “free” and “premium” combined together, and many of us have enjoyed using freemium apps on our phones, tablets and desktop devices over the years. The concept is quite simple, you find an app that is useful, and download the free version, mostly to see if it operates as advertised,… Read More

The Path Towards Automation of Analog Design

You may have noticed that I have been writing a lot more about analog design lately. This is no accident. Analog and custom blocks are increasingly important because of the critical role they play in enabling many classes of systems, such as automotive, networking, wireless, mobile, cloud, etc. Many of the SoCs needed for these… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era