For IC designs there are many data formats used throughout the logical and physical design process, and one of those file formats is called LEF, an acronym for Library Exchange Format, created by Tangent, an early EDA company with Place and Route tools that was acquired by Cadence way back in March 1989. LEF generation times can become… Read More

Electronic Design Automation

Cadence adds a new Fast SPICE Circuit Simulator

In the early years of Cadence their growth was bolstered through many well-timed acquisitions, however over the last several years I’ve noticed a distinctively different trend where they have internally developed EDA tools. I had a Zoom call with Jay Madiraju from Cadence, who markets their newly announced Fast SPICE … Read More

IoT’s Inconvenient Truth: IoT Security Is a Never-Ending Battle

The continued innovation and widespread adoption of connected devices — the internet of things (IoT) — has resulted in a vast range of conveniences that improve our lives every day. At the same time, the ubiquity of IoT devices, which market watchers estimate to be in the tens of billions, also makes it more attractive to bad actors… Read More

From Silicon To Systems

The annual Siemens Digital Industries Software user group event was held virtually on May 26th, which made it easy to attend from my home office, although selecting from the list of speakers was a challenge, because they offered 475 sessions, wow. My focus is EDA, so I listened to Joseph Sawicki, the Executive Vice President, IC … Read More

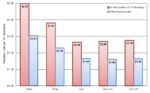

Heterogeneous Chiplets Design and Integration

Over the recent years, the volume and velocity of discussions relating to chiplets have intensified. A major reason for this is the projected market opportunity. According to research firm Omdia, chiplets driven market is expected to be $6B by 2024 from just $645M in 2018. That’s an impressive nine-fold projected increase over… Read More

Siemens EDA Acquires an IP Validation Tool for standard cells, IO and Hard IP

We’re living in an era of good growth for semiconductor design companies, and it’s no secret that each new SoC that comes along contains hundreds of IP blocks, so IP design re-use is just an accepted way of getting to market more quickly with lower risks. But how do we really know that all of the new IP is really correct? … Read More

Fuzzing to Validate SoC Security. Innovation in Verification

Fuzzing is to software verification what randomization is hardware verification. Can a fuzzing approach improve hardware security testing? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research ideas. As always, feedback… Read More

Safety Architecture Verification, ISO 26262

I love to read articles about autonomous vehicles and the eventual goal of reaching level 5, Full Automation, mostly because of the daunting engineering challenges in achieving this feat and all of the technology used in the process. The auto industry already has a defined safety requirements standard called ISO 26262, and one… Read More

WEBINAR: What Makes SoC Compiler The Shortest Path from SoC Design Specification to Logic Synthesis?

Defacto SoC Compiler whose 9.0 release was announced recently automates the SoC design creation from the first project specifications. It covers register handling, IP and connectivity insertion at RTL, UPF and SDC file generation right to logic synthesis. As part of the generation process of RTL and design collaterals, basic… Read More

CEO Interview: Toshio Nakama of S2C EDA

Toshio Nakama is the founder and the CEO of S2C and also a strong advocate of FPGA accelerated ASIC/SoC design methodology. Mr. Nakama devotes much of his time in promoting scalable Prototyping/Emulation hardware architecture and defining automated software specifications. He first started his career at Altera in 1997 and … Read More

Memory Innovation at the Edge: Power Efficiency Meets Green Manufacturing