A few times a year, I check in with AMIQ EDA co-founder Cristian Amitroaie to see what’s new with their company and the integrated development environment (IDE) market for hardware design and verification. Usually he suggests a topic for us to discuss, but this time I specifically wanted to learn more about the version of their Design… Read More

Electronic Design Automation

Calibre: Early Design LVS and ERC Checking gets Interesting

The last thing you want when taping out a design is to hit large numbers of violations in signoff checks that could have been flushed out and resolved in earlier flow iterations. For implementation flows (floorplanning, synthesis, place and route), it’s usual to do a lot of flow flushing work early in the design cycle and iteratively… Read More

Ask Not How FPGA Prototyping Differs From Emulation – Ask How FPGA Prototyping and Emulation Can Benefit You

The differences between commercial FPGA Prototyping (“Prototyping”) and Emulation have been well documented by the purveyors of commercial Prototyping and Emulation solutions, and the technical media. What has received less coverage is how Prototyping benefits differ from Emulation benefits. Both are intended to reduce… Read More

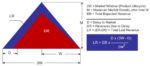

It’s Always About the Yield

Whether it is the stock market or the semiconductor market, the name of the game is yield. In semiconductors, yield has to do with minimizing scrap costs in all phases of manufacturing. This means squeezing as many good dies from a wafer as well as maximizing the number of good assembled/packaged chips that pass system level testing.… Read More

Configurable Processors. The Why and How

Configurable processors are hot now, in no small part thanks to RISC-V. Which is an ISA rather than a processor, but let’s not quibble. Arm followed with configurability in Cortex-X. Both were considerably preceded (a couple of decades) by Synopsys ARC® RISC CPUs and CEVA DSPs. Each stressed configurability as a differentiator… Read More

Architectural Planning of 3D IC

Before chiplets arrived, it seemed like designing an electronic system was a bit simpler, as a system on chip (SoC) methodology was well understood, and each SoC was mounted inside a package, then the packages for each component were interconnected on a printed circuit board (PCB). The emerging trend to design a 3D IC using chiplets… Read More

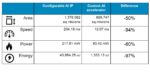

SoC Design Closure Just Got Smarter

Near the end of any large SoC design project, the RTL code is nearly finished, floorplanning has been done, place and route has a first-pass, static timing has started, but the timing and power goals aren’t met. So, iteration loops continue on blocks and full-chip for weeks or even months. It could take a design team 5-7 days… Read More

Your Symmetric Layouts show Mismatches in SPICE Simulations. What’s going on?

This Diakopto paper discusses for the first time, a new effect – a false electrical mismatch in post-layout simulations for perfectly symmetric nets. This effect is caused by the difference in distributions of parasitic coupling capacitors over the nodes of parasitic resistor networks, even for symmetric nets. This, in turn,… Read More

Pushing Acceleration to the Edge

As more AI applications turn to edge computing to reduce latencies, the need for more computational performance at the edge continues to increase. However, commodity compute engines don’t have enough compute power or are too power-hungry to meet the needs of edge systems. Thus, when designing AI accelerators for the edge, Joe… Read More

Why Use PADS Professional Premium for Electronic Design

My IC design career started just a few years before PADS got started in 1985 with a DOS-based tool for PCB design. A lot has changed since then, as PADS was acquired by Mentor Graphics in 2001, and continued to grow under Siemens EDA, now with four versions to choose from, where the top version is called PADS Professional Premium:

- PADS

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center