The last thing you want when taping out a design is to hit large numbers of violations in signoff checks that could have been flushed out and resolved in earlier flow iterations. For implementation flows (floorplanning, synthesis, place and route), it’s usual to do a lot of flow flushing work early in the design cycle and iteratively refine the design, constraints and flow settings to target a minimum TAT (turnaround time) pass through the final layout.

We need that same more iterative and interactive model for the signoff physical verification that has traditionally been done in batch mode on final designs. Increasing design and technology complexity are only making the circuit and physical verification tasks more challenging and time consuming. Design schedules and the need to work with designs with blocks in different design states force us to “shift left” more checks earlier in the design cycle.

While many layout-versus-schematic (LVS) circuit verification checks can be run earlier, running a full signoff set takes too long and includes thousands of transitory errors that will disappear in the final design and don’t need fixing – the run and debug time is excessive.

Siemens recognised the need for faster LVS iterations on dirty designs and identified the high impact errors that need cleaning in the early design stages. This led them to create Calibre nmLVS Recon (“Recon” is short for design reconnaissance here), initially supporting short isolation checks. That’s now been extended to support more checks.

A new Siemens EDA white paper describes how Calibre’s nmLVS Recon tool lets you target ERC and soft connection checks on incomplete and dirty designs while improving verification productivity and TAT.

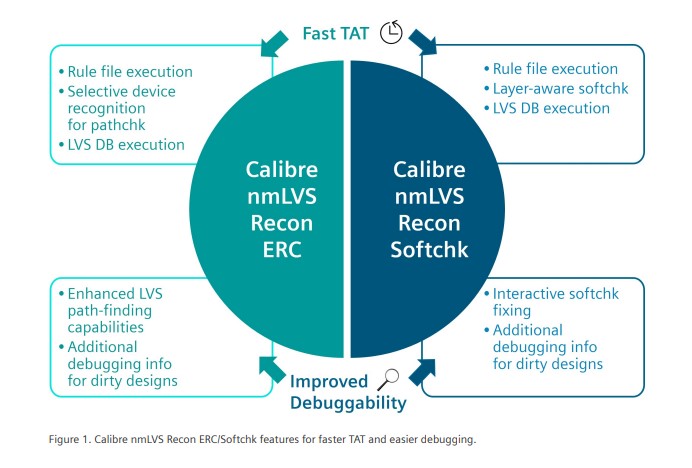

Figure 1 shows this new functionality:

This is a tool usage model that supports early stage design LVS and allows engineers to focus on the core of real and high impact design errors in the earlier design stages while avoiding trying to fix the thousands of transitory errors that will disappear as the design matures – avoidable engineering analysis and fixing time must not become the bottleneck.

The focus is on fast TAT for the targeted checks: runs can be started off existing LVS DBs and focused on only the required checks, giving dramatically faster LVS iterations on dirty designs.

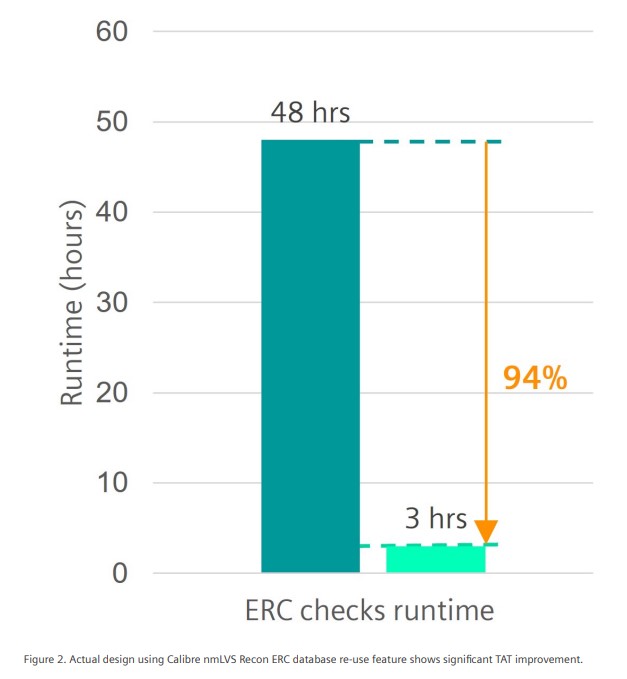

Rule file execution with selective device for path checking (pathchk) for ERC checks speeds up what can be a slow step for partially completed designs, while Enhanced LVS path-finding capability and debugging accelerates problem diagnosis and fixing. Starting ERC runs from previously generated LVS DBs means already completed steps need not be re-run and gives an efficient, incremental flow. Path isolation and enhanced reporting eliminate manual ERC debug steps.

Figure 2 shows the improvement in TAT possible when running standalone ERC checks from a reused DB:

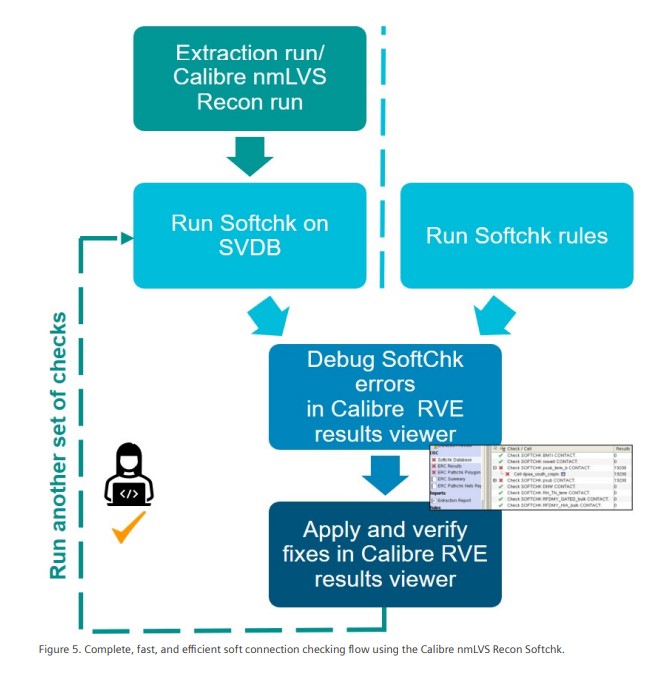

Soft connection checks are supported with the Calibre nmLVS Recon Softchk function with interactive debugging and improved debug to eliminate some previously manual steps. Rule decks can now be partitioned by layers of interest to save run time and memory and by layer groups for parallel processing. Again, we can reuse LVS databases from earlier LVS, extraction or Softchk runs to get faster incremental runs and skipping already completed checks like connectivity. The paper also notes that DB reuse could also be used in signoff to re-run only a single check.

Debug productivity is critical here and Calibre’s RVE debug interface (there’s a White Paper for this too) provides both interactive layout edits and fixes and immediate verification (Figure 5).

These new additions to Calibre nmLVS Recon usefully extend the range of early stage design LVS checking and Siemens continues to identify more of what it calls such “easy button” functionality so more verification can be run as early and efficiently as possible.

Find out more in the original white paper here:

Achieve dramatic productivity and turnaround time improvements in early design electrical rule checking

[also earlier White Papers on Calibre nmLVS Recon]

Accelerate time to market with Calibre nmLVS-Recon technology: A new paradigm for circuit verification

https://resources.sw.siemens.com/en-US/white-paper-accelerate-time-to-market-with-calibre-nmlvs-recon-technology-a-new-paradigm

Increase LVS verification productivity in early design cycles

https://resources.sw.siemens.com/en-US/white-paper-increase-lvs-verification-productivity-in-early-design-cycles

Siemens also has an interesting YouTube channel for Calibre:

https://www.youtube.com/user/ICNanometerDesign/featured?app=desktop

Also Read:

Architectural Planning of 3D IC

Pushing Acceleration to the Edge

Why Use PADS Professional Premium for Electronic Design

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.