As usual in January we start with a look back at the papers we reviewed last year. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome. And don’t forget to come see us at DVCon,… Read More

Electronic Design Automation

Arteris IP Acquires Semifore!

The semiconductor ecosystem consolidation continues with an interesting acquisition of an EDA company by an IP company. Having worked with both Arteris and Semifore over the past few years I can tell you by personal experience that this is one of those 1+1=3 types of acquisitions, absolutely.

Formal Datapath Verification for ML Accelerators

Formal methods for digital verification have advanced enormously over the last couple of decades, mostly in support of verification in control and data transport logic. The popular view had been that datapath logic was not amenable to such techniques. Control/transport proofs depend on property verification; if a proof is … Read More

How to Efficiently and Effectively Secure SoC Interfaces for Data Protection

Before the advent of the digitized society and computer chips, things that needed protection were mostly hard assets such as jewelry, coins, real estate, etc. Administering security was simple and depended on strong guards who provided security through physical means. Then came the safety box services offered by financial … Read More

Siemens Aspires to AI in PCB Design

This. AI in PCB design is not a new idea. Other PCB software companies also make that claim. But when a mainstream systems technology company like Siemens talks about the subject, that is noteworthy. They already have an adaptive user interface (UI) for their mechanical modeling suite and to assist in low-code development for application… Read More

Building better design flows with tool Open APIs – Calibre RealTime integration shows the way forward

You don’t often hear about the inner workings of EDA tools and flows – the marketing guys much prefer telling us about all the exciting things their tools can do rather than the internal plumbing. But this matters for making design flows – and building these has largely been left to the users to sort out. That’s an increasing challenge… Read More

Validating NoC Security. Innovation in Verification

Network on Chip (NoC) connectivity is ubiquitous in SoCs, therefore should be an attractive attack vector. Is it possible to prove robustness against a broad and configurable range of threats? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and… Read More

An Update on HLS and HLV

I first heard about High Level Synthesis (HLS) while working in EDA at Viewlogic back in the 1990s, and have kept watch on the trends over the past decades. Earlier this year Siemens EDA hosted a two day event, having speakers from well-known companies share their experiences about using HLS and High Level Verification (HLV) in their… Read More

Podcast EP132: The Growing Footprint of Methodics IPLM with Simon Butler

Dan is joined by Simon Butler, the founder and CEO of Methodics Inc, Methodics was acquired by Perforce in 2020, and he is currently the general manager of the Methodics business unit at Perforce. Methodics created IPLM as a new business segment in the enterprise software space to service the needs of IP and component based design.… Read More

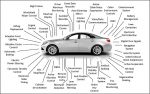

Functional Safety for Automotive IP

Automotive engineers are familiar with the ISO 26262 standard, as it defines a process for developing functional safety in electronic systems, where human safety is preserved as all of the electronic components are operating correctly and reliably. Automotive electronics have now grown to cover dozens of applications, and… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center