Walking the exhibit floors at DAC in December I spotted the familiar face of Anupam Bakshi, Founder and CEO of Agnisys, so I stopped by the booth to get an update on his EDA company. My first question for him was about the origin of the company name, Agnisys, and I found at that Agni means Fire in Sanskrit, one of the five elements.

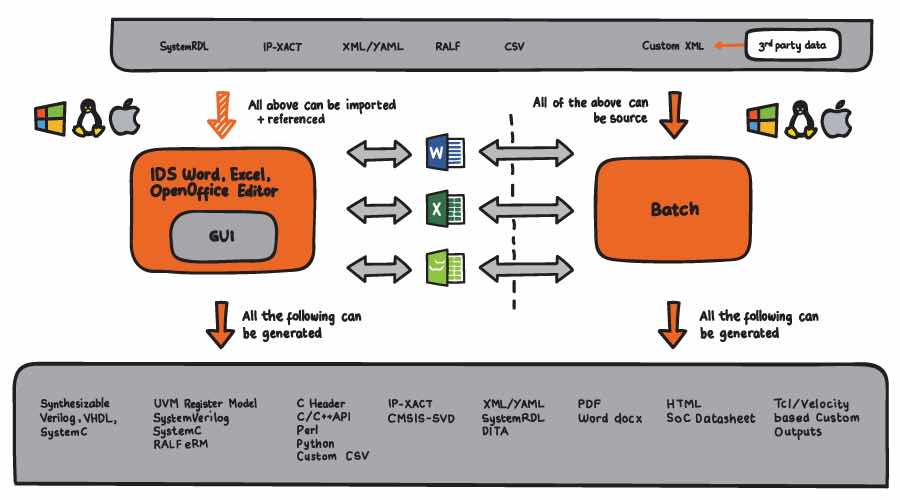

The company vision is the same today as it was from the founding, it’s a tool flow going from the specification to implementation, across design and verification and SW and device drivers. Having a single source of truth on registers for all engineering groups to know and use is a core idea. IDesignSpec is their EDA tool launched 11 years ago now, and the scope of the tool has only grown over time.

There are now resellers of Agnisys tools in all continents, the number of licenses have been going up, and the new trend is for site licensing, instead of having just a handful of licenses on one project. When one IC design team starts using IDesignSpec, then other adjacent teams start to hear about the benefits and want to give it a try on their project too.

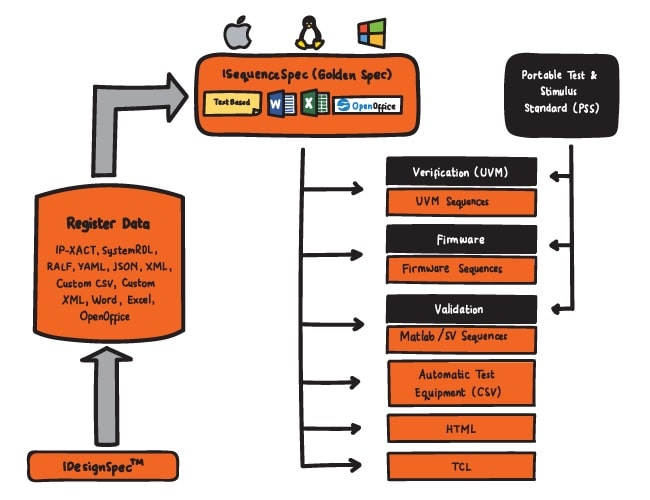

Another EDA tool at Agnisys is called ISequenceSpec, released about three years ago, and it helps engineers to capture sequences as stimulus generation used in verification, firmware and even post-silicon validation. ISequenceSpec can convert into UVM or C levels. Here’s where ISequenceSpec fits into a design flow:

The newest EDA tool has taken a totally different approach to introduction, because it is being crowd-sourced, and it’s called ISpec.ai. What’s unique is that this tool automatically converts English assertions into proper SystemVerilog Assertions (SVA) by using Machine Learning (ML) techniques. So the company finds out what engineers think about when learning SVA, and then the users can give Yes (Green) or No (Red) feedback, leaving any comments about the quality of the conversion. This tool was released about 2-3 months ago, then existing customers became aware of it and started testing, and so far about 200 engineers have provided feedback.

They have even offered quizzes to see if engineers can answer questions about SVA with or without using iSpec.ai, which is kind of fun and technical at the same time. So this tool in a way is kind of similar to Google Translate, as it translates in both directions, both into SVA or English. The company plans to productize this web-based tool after a learning phase.

DVCon US 2022 is coming up in February, and Agnisys has a paper on the iSpec.ai tool, so consider attending that online event to see what progress has been made so far.

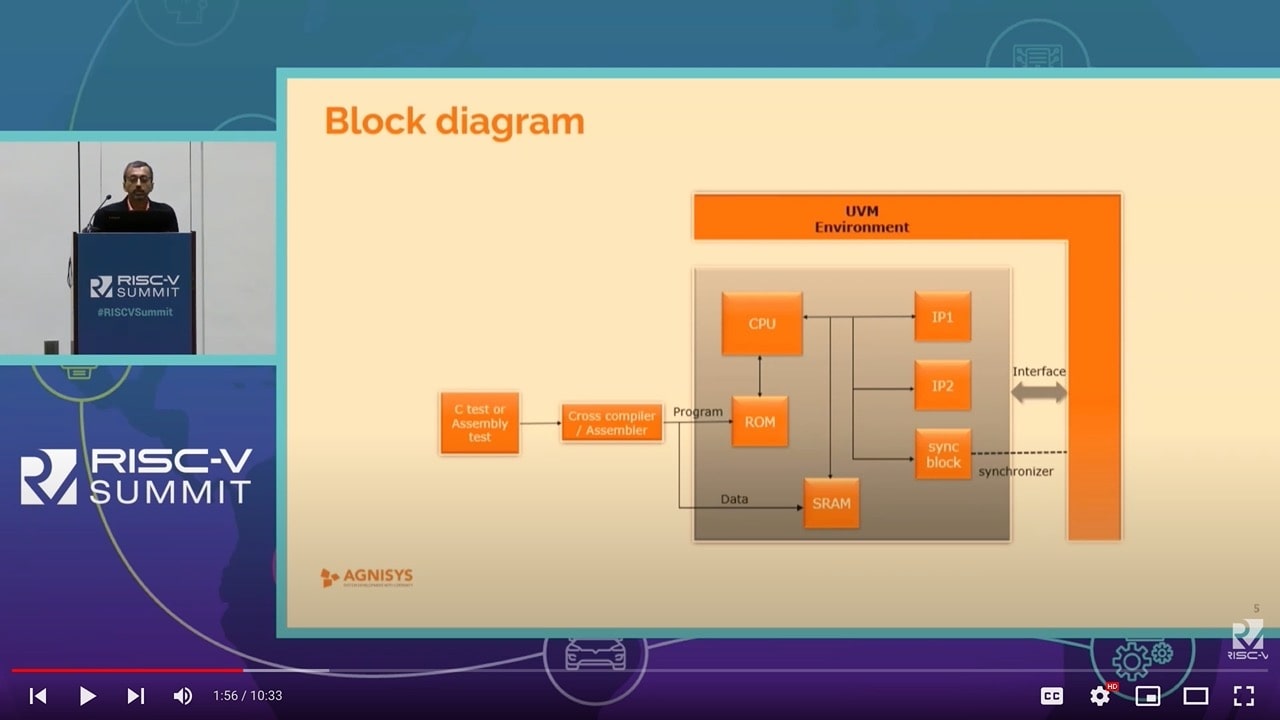

Co-located with DAC this year was the RISC-V conference, and Agnisys presented on, “A System Level Verification and Validation Environment using SweRV”. You can watch this 10 minute presentation on YouTube, and it was a Lightning Talk. SweRV is an open-source RISC-V core from Western Digital.

Connecting all of the semiconductor IPs together in a system-level environment, your team either does this by hand or with some automation. Using SweRV as the processor you can then connect together tests at the IP or system level. Using the C to UVM interface, then both levels can talk together. The processor knows C, while the other IPs understand UVM. So you can run your C program, and it then causes UVM transactions by the tool using SweRV.

Another new tool in 2021 is called IDS-FPGA, now part of the IDesignSpec family, so that FPGA design teams can reduce their development times by using an approach with automated code generation, IP generators, and have an integrated flow with FPGA vendor software. They support the Xilinx UltraScale+ IP-based design development, and have integration with Xilinx Vivado and the Intel Quartus Prime architectures.

Summary

Agnisys has a 15 year history in providing their IDesignSpec tool, and it just keeps getting more robust each year. This company is one of the very few EDA vendors that actually demonstrates their tool live, running on a laptop, so it wasn’t just a PowerPoint presentation at DAC. I think that engineers are really attracted to seeing an EDA tool running live, because they are curious at how the GUI looks, how quickly it operates, and how intuitive the flow is.

Also read:

What the Heck is Collaborative Specification?

AUGER, the First User Group Meeting for Agnisys

Share this post via:

Solving the EDA tool fragmentation crisis