Access to sophisticated RF EDA tools is one thing. Effectively harnessing their capability in real-world use is another. Digital EDA and test & measurement providers have long recognized ongoing customer education needs for their solutions. Keysight is embarking on an initiative to develop curated EDA experiences with… Read More

Electronic Design Automation

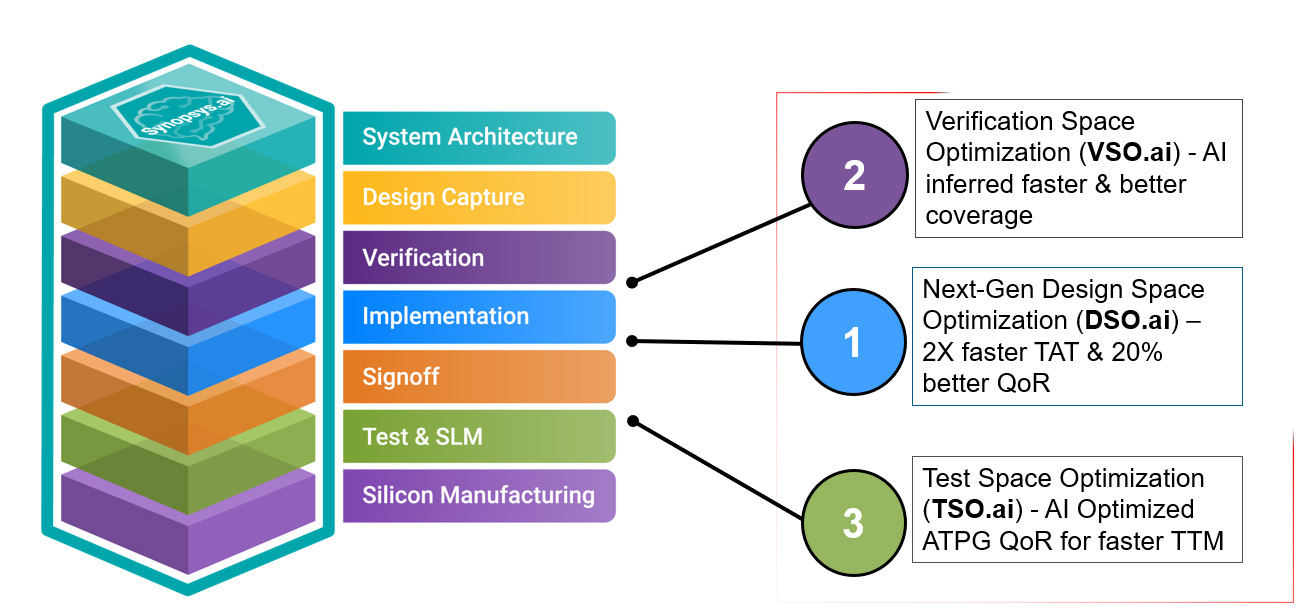

WEBINAR: Leap Ahead of the Competition with AI-Driven EDA Technology

The demands on today’s designs are relentless. Each generation of devices needs to be faster, smaller, more functional, more connected and more secure than the previous generation. In the face of all this, the time required for next-generation devices to hit the market is dramatically shrinking. That means the competitive landscape… Read More

Siemens Enhances Supply Chain Visibility with Real-Time Intelligence for its Xcelerator Platform

Next generation electronic systems require an engineering approach incorporating a digital twin methodology for early verification with digital prototypes. Over the course of a design project, the digital twin model evolves to allow more complex interactions including analysis, simulations and validations earlier… Read More

Are you Aware about Risks Related to Soft Errors?

Soft errors change stored data and cause temporal malfunctions in electronic systems. This mainly occurs when radiation particles collide with semiconductor devices. Soft errors are a concern in all environments, whether in the atmosphere, in space, or on the ground.

Soft errors are critical in high-reliability applications… Read More

AMIQ: Celebrating 20 Years in Consulting and EDA

We’re getting close to the annual July Design Automation Conference (DAC) in San Francisco, and every year I like to make the rounds of the exhibitors beforehand and see what’s new. When I checked with AMIQ EDA, I found that this is a big year for them. Their parent company AMIQ just reached its 20th anniversary, and they’ll be celebrating… Read More

Visit with Agnisys at DAC 2023 in San Francisco July 10-12

I’d like to extend an invitation to you and your development team to visit with Agnisys in our booth, #2512, at this week’s Design Automation Conference (DAC) 2023, Monday, July 10-12.

In its 60th year, DAC is recognized as the premier event for the design and design automation of electronic chips to systems, so you can count on team… Read More

Defacto Celebrates 20th Anniversary @ DAC 2023!

Defacto Technologies is a company that specializes in Electronic Design Automation (EDA) software and solutions. Defacto offers a range of EDA software solutions that help streamline and optimize various stages of the front-end design process. Their tools focus on chip design assembly and integration before logic synthesis

Computational Imaging Craves System-Level Design and Simulation Tools to Leverage AI in Embedded Vision

Aberration-free optics are bulky and expensive. Thanks to high-performance AI-enabled processors and GPUs with abundant processing capabilities, image quality nowadays relies more on high computing power tied to miniaturized optics and sensors. Computational imaging is the new trend in imaging and relies on the fusion … Read More

Is Your RTL and Netlist Ready for DFT?

I recall an early custom IC designed at Wang Labs in the 1980s without any DFT logic like scan chains, then I was confronted by Prabhu Goel about the merits of DFT, and so my journey on DFT began in earnest. I learned about ATPG at Silicon Compilers and Viewlogic, then observability at CrossCheck where I met Jennifer Scher, now she’s… Read More

Better Randomizing Constrained Random. Innovation in Verification

Constrained random methods in simulation are universally popular, still can the method be improved? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome.… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry