Much of the recent Keysight EDA 2024 announcement focuses on high-speed digital (HSD) and RF EDA features for Advanced Design System (ADS) and SystemVue users, including RF System Explorer, DPD Explorer (for digital pre-distortion), and design elements for 5G NTN, DVB-S2X, and satcom phased array applications. Two important… Read More

Electronic Design Automation

Assertion Synthesis Through LLM. Innovation in Verification

Assertion based verification is a very productive way to catch bugs, however assertions are hard enough to write that assertion-based coverage is not as extensive as it could be. Is there a way to simplify developing assertions to aid in increasing that coverage? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl … Read More

Version Control, Data and Tool Integration, Collaboration

As a follow up from my #60DAC visit with Simon Rance of Keysight I was invited to their recent webinar, Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration. Karim Khalfan, Director of Solutions Engineering, Data & IP Management was the webinar presenter.

Modern… Read More

WEBINAR: Emulation and Prototyping in the age of AI

Artificial Intelligence is now the primary driver of leading edge semiconductor technology and that means performance is at a premium and time to market will be measured in billions of dollars of revenue. Emulation and Prototyping have never been more important and we are seeing some amazing technology breakthroughs including… Read More

Power Supply Induced Jitter on Clocks: Risks, Mitigation, and the Importance of Accurate Verification

In the realm of digital systems, clocks play a crucial role in synchronizing various components and ensuring smooth flow of logic propagation. However, the accuracy of clocks can be significantly affected by power supply induced jitter. Jitter refers to the deviation in the timing of clock signals with PDN noise compared to ideal… Read More

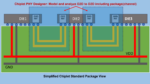

Optimizing Shift-Left Physical Verification Flows with Calibre

Advanced process nodes create challenges for EDA both in handling ever larger designs and increasing design process complexity.

Shift-left design methodologies for design cycle time compression are one response to this. And this has also forced some rethinking about how to build and optimize design tools and flows.

SemiWiki… Read More

Power Analysis from Software to Architecture to Signoff

SoC designs use many levels of design abstraction during their journey from ideation to implementation, and now it’s possible to perform power analysis quite early in the design process. I had a call with William Ruby, Director of Porduct Marketing – Synopsys Low Power Solution to hear what they’ve engineered… Read More

WEBINAR: Why Rigorous Testing is So Important for PCI Express 6.0

In the age of rapid technological innovation, hyperscale datacenters are evolving at a breakneck pace. With the continued advancements in CPUs, GPUs, accelerators, and switches, faster data transfers are now paramount. At the forefront of this advancement is PCI Express (PCIe®), which has become the de-facto standard of interconnect… Read More

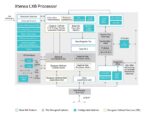

Cadence Tensilica Spins Next Upgrade to LX Architecture

When considering SoC architectures it is easy to become trapped in simple narratives. These assume the center of compute revolves around a central core or core cluster, typically Arm, more recently perhaps a RISC-V option. Throw in an accelerator or two and the rest is detail. But for today’s competitive products that view is a … Read More

Inference Efficiency in Performance, Power, Area, Scalability

Support for AI at the edge has prompted a good deal of innovation in accelerators, initially in CNNs, evolving to DNNs and RNNs (convolutional neural nets, deep neural nets, and recurrent neural nets). Most recently, the transformer technology behind the craze in large language models is proving to have important relevance at… Read More

Solving the EDA tool fragmentation crisis