Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More

Electronic Design Automation

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More

What I Learned About FPGA-based Prototyping

Today I attended an Aldec webinar about ASIC and SoC prototyping using the new HES-7 Board. This prototyping board is based on the latest Virtex-7 FPGA chips from Xilinx.

You can view the recorded webinar here, which takes about 30 minutes (should be available in a few days). I first blogged about the HES-7 two months ago, ASIC Prototyping… Read More

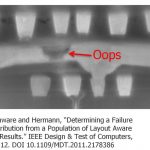

Test and Diagnosis at ISTFA

Finding and debugging failures on integrated circuits has become increasingly difficult. Two sessions at ISTFA (International Symposium for Testing and Failure Analysis) on Thursday address the current best practices and research directions of diagnosis.

The first was a tutorial this morning by Mentor Graphics luminary… Read More

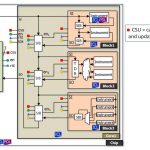

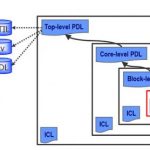

Creating Plug-and-Play IP Networks in Large SoCs with IEEE P1687 (IJTAG)

Until now, the integration and testing of IP blocks used in large SOCs has been a manual, time consuming design effort. A new standard called IEEE P1687 (or “IJTAG”) for IP plug-and-play integration is emerging to simplify these tasks. EDA tools are also emerging to support the new standard. Last week mentor announcedTessent IJTAG,… Read More

The logic of trusting FPGAs through DO-254

Any doubters of the importance of FPGA technology to the defense/aerospace industry should consider this: each Airbus A380 has over 1000 Microsemi FPGAs on board. That is a staggering figure, especially considering the FAA doesn’t trust FPGAs, or the code that goes into them.… Read More

Jasper User Group Keynotes

I attended the Jasper User Group this week, at least the keynotes, the first by Kathryn Kranen the CEO of Jasper and the second by Bob Bentley of Intel.

Kathryn went over some history, going back to when the company was started (under the name Tempus Fugit) back in August 2002 with a single product for protocol verification. Now, since… Read More

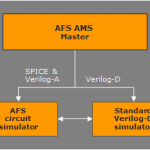

Analog FastSPICE AMS — Simple, Fast, nm-Accurate Mixed-Signal Verification

Verification and AMS are top search terms on SemiWiki so clearly designers have a pressing need for fast and accurate verification of today’s mixed-signal SoCs that include massive digital blocks and precision analog/RF circuits. They need simulation performance to verify the mixed-signal functionality, and they need nanometer… Read More

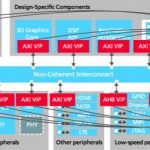

Cadence sets the Global Standards in VIP for AMBA based SoC

We have shown in Semiwiki how strong Cadence position was in Verification IP (VIP) in a previous post focusing on Interface standards like SuperSpeed USB or PCI Express. But IP based functions are used everywhere in a SoC, not only to interface with the external world, and need to be verified, as well, like for AMBA based functions.… Read More

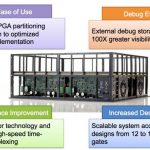

Next Generation FPGA Prototyping

One technology that has quietly gone mainstream in semiconductor design is FPGA prototyping. That is, using an FPGA version of the design to run extensive verification. There are two approaches to doing this. The first way is simply to build an prototype board, buy some FPGAs from Xilinx or Altera and do everything yourself. The… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior