After a show like DesignConwraps up we get a chance to ask ourself what it all meant, and how was this year different than last year. Reading through many posts about DesignCon I came to discover that the Awards at DesignCon are less contentious than at CES, and also that ANSYSreceived a DesignVision awardfor the 2nd year running. … Read More

Electronic Design Automation

Notes from Common Platform: Collaborate or Die

FinFETs are hot, carbon nanotubes are cool, and collaboration is the key to continued semiconductor scaling. These were the main messages at the 2013 Common Platform Technology Forum in Santa Clara.

The collaboration message ran through most presenations, like the afternoon talk by Subi Kengeri of GLOBALFOUNDRIES and Joe Sawicki… Read More

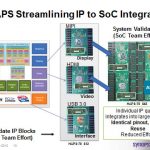

Using Soft IP and Not Getting Burned

The most exciting EDA + Semi IP company that I ever worked at was Silicon Compilers in the 1980’s because it allowed you to start with a concept then implement to physical layout using a library of parameterized IP, the big problem was verifying that all of the IP combinations were in fact correct. Speed forward to today and our… Read More

RTL Clock Gating Analysis Cuts Power by 20% in AMD Chip!

Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the… Read More

UVM: Lowering the barrier to IP reuse

One of my acquaintances at Intel must have some of the same viewing habits I do, based on a recent Tweet he sent. He was probably watching “The Men Who Built America” on the History Channel and thinking as I have a lot recently about how the captains of industry managed to drive ideas to monopolies in the late 1800s and early 1900s.

… Read MoreDifference

Sanjiv Kaul is New CEO of Calypto

Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

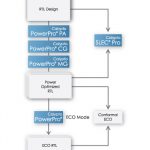

Software Driven Power Analysis

Power is a fundamentally hard problem. When you have finished the design, you have accurate power numbers but can’t do anything about them. At the RTL level you have some power information but it is often too late to make major architectural changes (add an offload audio-processor, for example). Early in the design, making… Read More

Help, my IP has fallen and can’t get up

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

A Brief History of ClioSoft

In the 1990s, software developers were established users of software configuration management (SCM) tools such as open source RCS/CVS or of commercial systems such as Clearcase. Hardware designers, however, managed design data in ad hoc home-grown ways. ClioSoft’s founder, Srinath Anantharaman, recognized that hardware… Read More

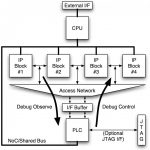

Seeing inside SoC designs, from the beginning

Engineers have this fascination with how things work. They are thrilled to tear stuff apart, and sometimes to even be able to put it back together afterwords. So I can keep my recovering engineer card, I thought I’d take a few moments and look inside a technology Daniel Payne and I have been covering here, exploring where the idea started… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!