You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4380

[filter] => raw

[cat_ID] => 157

[category_count] => 4380

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

First, I wish there were more conferences/workshops like this. This is much more about sharing ideas and brainstorming than the stark commercialism of DAC. I presented Atrenta’s role in enabling 3[SUP]rd[/SUP]-party IP qualification for the TSMC soft IP library.

My presentation slides are located here:

http://www.eda.org/edps/Papers/5-3%20Bernard%20Murphy.pdf… Read More

Since I started looking at the ways Texas Instrumentsworks through its strategies, my belief is getting firmed up that this is one company which can always sail through rough waters during downturn and reap rich benefits during upturn. They regularly review their strategies and can predict ahead of time when the water is about … Read More

Please join me for an IP conversation in collaboration with ClioSoft on Wednesday, April 30th, 2014 @ 11:00 AM PST. At the EDPS Workshop IP day there were two interesting presentations on IP reuse. The first one was by Warren Savage of IPextreme: Top Ten Reasons Why Internal IP Reuse Fails. The second was by Ranjit Adhikary of ClioSoft:… Read More

Designing an SoC requires a team, and the engineers typically use lots of specialized EDA software and semiconductor IP to get the job done. Many have started to ask about how designing a chip is different than designing and managing a large software project, or how is analog design different than digital design in terms of managing… Read More

Welcome, LPDDR4!by Eric Esteve on 04-23-2014 at 3:46 amCategories: IP, Synopsys

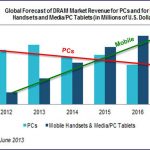

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

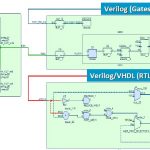

Learning an HDL language or an HDL simulator are two different things, so I wanted to see what was available for learning a vendor-specific HDL simulator. I’ve already taught Verilog as an instructor using both ModelSim and Active-HDL simulators, however we only used a handful of commands in the class and labs in order to … Read More

“Failure to plan is planning to fail.” If that is true – and it has been quoted verbatim or slightly modified so many times throughout modern history, there has to be some truth – why does most of the engineering community seem to detest planning so much?

Engineering planning doesn’t mean whipping out a block diagram or pseudo code,… Read More

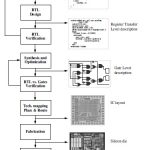

In an era of SoCs with millions of gates, hundreds of IPs and multiple ways to verify designs through several stages of transformations at different levels of hierarchies, it is increasingly difficult to handle such large data in a consistent and efficient way. The hardware and software, and their interactions, have to be consistent… Read More

In a complex world of SoCs with multi-million gates and IPs from several heterogeneous sources, verification of a complete semiconductor design has become extremely difficult, and it’s not enough. In order to ascertain the right intent of the design throughout the design cycle, debugging at various stages of the design cycle… Read More

Cadence announced today that it is acquiring Jasper Design Automation for $170M in an all-cash offer. Jasper has $24M in cash so it is really an acquisition for around $145M. i think that is around 4X revenue but I only know rumors about Jasper’s revenue numbers.

All the big 3 already have their own formal technology but the … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center