Paul McLellan was on assignment in Hong Kong last week so I attended the Linley Mobile Conference and was not surprised Intel did not present. During the networking sessions I asked more than a dozen people why and the answers were pretty focused on “Intel still does not play well with others” and “Intel’s current mobile offerings… Read More

Electronic Design Automation

The Matrix, your ultimate OPC

One of the many consequences of shrinking process nodes is that traditional OPC can no longer achieve good pattern fidelity with reasonable turn-around-time. But there is a solution; we made it ourselves and call it matrix OPC.

First, let’s explore the problems with traditional optical proximity correction (OPC) when applied… Read More

IC Power Noise Reliability for FinFET Designs

Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused… Read More

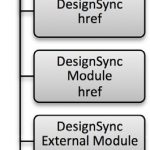

Flexible Integration System for IPs into SoC

The number of IPs with growing complexity and heterogeneity is ever increasing (counting into hundreds) to be integrated into a single SoC. It’s not possible to have them all available at once and in a single repository for the integration engineers to assemble all of them together and integrate into the SoC. The reality is that … Read More

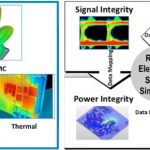

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

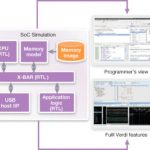

Hardware/Software Debug

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

Leveraging Design Team Energy!

Once upon a time, in 1987 to be specific, a French design team was trying to develop a 100% Made in France supercomputer. In fact, not really 100%, as the CPU chips were supposed to be made by Weitek, but we never saw any of these chips, probably too challenging to be designed right first time! Anyway, I was in charge of the design of the … Read More

Aldec is Celebrating 30 Years @ #51DAC!

Dr. Stanley Hyduke founded Aldec in 1984 and their first product was delivered in 1985, named SUSIE (Standard Universal Simulator for Improved Engineering), a gate-level, DOS-based simulator. The SUSIE simulator was priced lower than other EDA vendor tools from the big three: Daisy, Mentor and Valid (aka DMV). Today, Aldec … Read More

More “toddlers” innovating on the IoT

As the PC Era took shape, Tom Peters predicted the shift away from “where all the cars are parked”. He foresaw that large, established companies would no longer be the economic engine, or the dominant force in innovation. Smaller firms, even individuals, would rise to prominence in a new, technologically-driven economy.

That … Read More

Eric Esteve to Present during CDN Live 2014 in Munich

I will have the privilege to give an “IP Outlook” presentation during next Cadence event in Europe, CDN-Live to be held in Munich the 19[SUP]th[/SUP] to 21[SUP]st[/SUP] of May. I had a look at the agenda, and the conference will be pretty busy, especially on Tuesday, as there will be more than fifty presentations, starting at 10:30… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center