In 2002, MunEDA was launched under the guidance of EDA academic veterans and IEEE fellows Prof. Kurt Antreich and Prof. Helmut Gräb (TUM Munich Technical University ) which represented 20 plus years of EDA research and experience. All MunEDA tools are combined in a tool suite called WiCkeD[SUP]TM[/SUP]. The tool suite brand was… Read More

Electronic Design Automation

Teach Yourself Silvaco

In the dim and distant past, if you wanted to learn how to use a particular EDA tool then you would go on a training course. This would often be multiple days and often a significant dollar investment too. For most EDA companies, that option still exists and the big 3 have quite extensive training catalogs.

But nowadays it is often easier… Read More

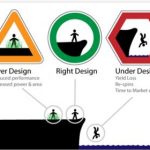

Solido Patent Enabling Variation-Aware Custom IC Design

This is patent number twelve for Solido Design Automation THE leading provider of variation analysis and design software for high yield and performance IP and system-on-chip (SOCs). Additional patents are pending on high-sigma analysis, high-dimensional data mining, and other technologies to design and verify custom integrated… Read More

New Frontiers in MEMS and Their Enablers

With the 51[SUP]st[/SUP] DACapproaching quickly, I spent some time last week-end to look around about what new trends, technologies and innovations will be most talked about during DAC. Every year, I find some exciting new technologies in the semiconductor industry and the overall semiconductor ecosystem that get wider exposure… Read More

Is the Chief IoT Barrier Privacy?

The World Affairs Council event, The Internet of Things: Global Implications of Merging the Physical and Digital Worlds, was hosted by Cadence last week. One thing I can tell you is that Cadence sure does know how to throw a party! They had me at free food and beer but the topic was also of great interest since my next project will involve… Read More

Mentor @ #51DAC Must See!

We’ve packed each day full of exciting activities focused on the latest in cutting-edge design. Use this site to find your favorite Mentor experts and events—whether in our suites and networking events, at our partner booths or in the conference. You won’t want to miss a thing!

Celebrating Your Design Creativity!

Rejuvenate with… Read More

Dassault #51DAC Assault!

This is one of the most aggressive DAC appearances I have seen from Dassault, absolutely. Dassault Systèmes is branded as the: 3D EXPERIENCE Company that provides virtual universes to imagine sustainable innovations. Its world-leading solutions transform the way products are designed, produced, and supported. Dassault … Read More

Selecting the Right Standard Cell & Memory for 28HPM DSP core: real case with CEVA XC4210

Listening to a webinar at your desk, in front of a PC screen will never replace a live presentation, but the lesson learned to time spent ratio can be incredibly higher than when traveling to a conference to listen several presentation. If you are interested by the approach taken by a complex DSP design team to overcome the various … Read More

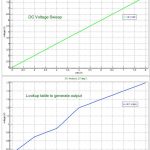

Analog and Full Chip Simulation at Micron

IDM companies like Micronuse SPICE circuit simulators during the design phase in order to predict timing, currents and power on their custom IC chip designs at the transistor level. A senior memory design engineer at Micron named Raed Sabbahtalked today at a webinarabout how the embedded solutions group uses the FineSimcircuit… Read More

What Executives Say About IP Licensing

In the fabless world of semiconductor design, IP components have become indispensable partners and have enabled the development of complex billion gate SoCs. IP business in general is exhibiting a very high growth rate since couple of years and it is going to increase; the same is being reflected by a growing number of IP vendors… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center