Something happened this morning that doesn’t happen too much any more: a new EDA company came out of stealth mode and announced its product line. The company is Invionics, and they are based in Vancouver BC. The CEO is Brad Quinton who largely funded the company himself, although with some grants from the Canadian government.… Read More

Electronic Design Automation

Analyzing Cortex-A53 octa-core on Linux

Octa-core sells smartphones and tablets. 64-bit ARM Cortex-A53 implementations are available from Huawei, MediaTek, Qualcomm, Samsung, and now Marvell, with Rockchip and others on the way. Suddenly, almost everyone planning to run Linux is being asked for octa-core designs.

If it were easy, anyone could do it. Increasing … Read More

Semiconductor IP Make the World Go Round!

Semiconductor IP really does make the life of a semiconductor professional much easier which is why Google brings us so much IP traffic. If you look at the SemiWiki analytics, IP has always been a top draw. In comparison to standard EDA traffic, IP gets about 25% more views per blog on average. Synopsys is not only the leading EDA company… Read More

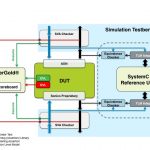

Complete SoC Debugging & Integration in a Single Cockpit

These days it’s common to expect large digital designs, analog blocks, custom IPs, glue logic, interfaces and interconnects all developed separately, perhaps by different vendors / teams, but integrated together in a single environment forming an SoC. The SoC can have multiple clock domains and can work in multiple modes of … Read More

Are you SmarCoT or IoT?

No need to explain the IoT acronym (Internet of Things) except that IoT doesn’t really describe a reality: do you really know about any “Thing” being directly connected to the Internet? In fact, there is probably some intermediate system linking this thing with the Cloud, like a smartphone, an Internet box, a PC, etc. Just take a … Read More

Semiconductor IP Information Flow!

One of the biggest challenges in the IP business, or any other business for that matter, is managing the information flow. Semiconductor IP is a critical piece of the fabless semiconductor ecosystem so anybody and everybody can write about it. Unfortunately, anybody and everybody ARE writing about it. From day one IP has been a … Read More

How many 28nm FDSOI SoC Design Starts in 2015? In 2020?

I would like to further discuss this graphic (presented during IP-SoC 2014 by John Koeter, VP of Marketing IP and prototyping, Synopsys) and focus on Active Design and Tapeouts at 28nm. In fact the very first activity appeared in Q1 2007, but it was only during 2010 that 28nm become popular, after the first Tapeouts coming in Q1 and… Read More

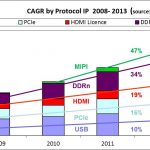

IP-SoC 2014 Top Class Presentations…

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

Using Cadence PVS for Signoff at TowerJazz

TowerJazzis a specialty foundry that provides IC manufacturing into several markets, like: RF, high-performance analog, power, imaging, consumer, automotive, medical, industrial and aerospace/defense. In June there was a presentation from Ofer Tamir of TowerJazz at DACin the Cadence theatre, so I had a chance this week … Read More

How Sonics Uses Jasper Formal Verification

The Jasper part of Cadence announced jointly with Sonics a relationship whereby Sonics uses JasperGold Apps as part of their verification. I talked to Drew Wingard, the CTO, about how they use it.

One way is during the day when their design engineers use Jasper as part of their verification arsenal. Interestingly it is the design… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior