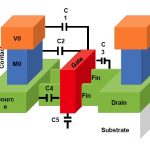

We read about FinFET technology in the semiconductor press daily now, thanks to Intel introducing their TriGate transistors starting in 2011 and creating a race with foundries and IDMs to switch from planar CMOS nodes. To get some perspective about the progress of FinFET IP and EDA tools I spoke with two experts from Synopsys, Swami… Read More

Electronic Design Automation

Why did Mentor Acquire Tanner EDA?

You have to love when a professional journalist leaks a story and cites a “source close to the acquisition.” News flash: Anyone “close” to the acquisition is under NDA which is a legally binding agreement, not very professional if you ask me. Bloggers however can write whatever they want but since I was actually “close” to … Read More

Voltage Limbo Dancing: How Low Can You Go?

All chips these days have to worry about power. Indeed it is typically the top of the priority list of concerns, above performance and even area. Transistors are effectively fast and free, but you can’t have too many of them (at least turned on at once). The most obvious way to reduce power is to lower the supply voltage. This … Read More

Is Cadence the Best EDA Company to Work for?

Apparently that is the case. Honestly my choice would have been Mentor but I can easily make an argument for Cadence based on my discussions with the foundries and their top customers but more on that later.

Fortune Magazine last week added Cadence to the 2015 list of “100 Best Companies to Work For” citing a cultural transformation… Read More

Three Colorful Bytes from the NXP History

The proposed merger of NXP and Freescale, which creates a bigger semiconductor outfit, also brings forth some fascinating history bytes from the technology heritage that these two spin-offs carry from their respective corporate parents. In 2006, Philips Electronics sold its chip business division Philips Semiconductors… Read More

Synflow and Cx

When hardware designers hear about a new language their heart sinks. We already have Verilog, SystemVerilog and VHDL. And if you go up a level, we have C, C++ and SystemC. Isn’t that enough? However, if you tell a software engineer about a new language they are interested, there are hundreds of programming language and hundreds… Read More

CDN is Live in Silicon Valley!

As big of a fan as I am of Social Media there is still nothing like getting up close and personal when collaborating with the fabless semiconductor ecosystem. After 30+ years in Silicon Valley if there is one thing I have learned it’s that “showing up” is the #1 key to success, absolutely.

Speaking of showing up, each year there are three… Read More

Exensio: Big Data in the Fab

For 20 years PDF Solutions have been working with fabs on yield enhancement. Today, they announced their Exensio Platform for big data manufacturing environments. They haven’t really been keeping it a secret and have been talking about it at events since late last year, but it has basically been in stealth mode for the last… Read More

Simple Analog ASIC Solves Thermal Analysis Problems

In a world where Application Specific Integrated Circuits (ASICs) and Application Specific Standard Products (ASSPs) are dominating every conceivable application, greater attention is being applied to their long term reliability. These chips are being built on smaller lithographies, running at higher speeds, dissipating… Read More

DAC: March Update

DAC is coming up. It is already March. If you are in the EDA industry then it is basically three months away, which sounds a lot until you actually have to get everything pulled together so that your booth is ready to go on Monday June 7[SUP]th[/SUP]. Exhibit hours have been extended and now run from 10am to 7pm (only until 6pm on Wednesday).… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era