Starvision Pro from Concept Engineering is a bit like one of those Leatherman multi-tools, it has a huge number of different functions, some of them fairly specialized but nonetheless incredibly useful. Many of these functions are unique to Starvision Pro, with nothing else like it on the market. Some new videos, produced by EDA… Read More

Electronic Design Automation

Mapping Focus and Dose onto BEOL Fabrication Effects

With today’s ArF based lithography using 193nm wavelength light, we are hard up against the limitations imposed by the Raleigh equation. Numerous clever things have been devised to maximize yield and reduce feature size. These include 2 beam lithography, multiple patterning, immersion litho processes to improve NA, thinner… Read More

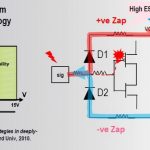

Lake Tahoe: The Center of ESD Innovation

Almost anyone that is active in IC design will be “in touch” with Electrostatic Discharge (ESD) at some time (pun intended). Preventing ESD related IC failures remains something like black magic—at least it’s easy to get that feeling when you are trying to debug ESD failures. I/O and ESD layouts that resulted in excellent robustness… Read More

Shifting Chip Design Left!

In the traditional sense “Shift Left” is the process of making things simpler in an effort to make things faster. Shift Left was the theme of theDVCon keynote last week delivered by Synopsys co-founder and co-CEO Aart de Geus which is right on topic when it comes to modern semiconductor design and manufacturing, absolutely.

KEYNOTE:… Read More

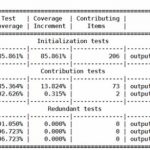

CDC Verification: A Must for IP and SoCs

In the modern SoC era, verification is no longer a post-design activity. The verification strategy must be planned much earlier in the design cycle; otherwise the verification closure can become a never ending problem. Moreover, verification which appears to be complete may actually be incomplete because of undetected issues… Read More

Cadence’s New Implementation System Promises Better TAT and PPA

On Tuesday Cadence made a big announcement about their new physical implementation offering, Innovus, during the keynote address at the CDNLive event in Silicon Valley. Cadence CEO Lip-Bu Tan alluded to it during his kick off talk, and next up Anirudh Devgan, Senior Vice President, Digital & Signoff Group, filled in more … Read More

How many coats cover this SoC?

“Most interior paint covers with one coat.” Back when there was something called a newspaper, this was an actual blurb in the home improvement pages, section 3, part 8, page 5 of the Chicago Tribune on Sunday, August 13, 1961. Even then, marketers were catering to consumers looking to cut corners and save time, and one-coat coverage… Read More

SoCs More Vulnerable to ESD at Lower Nodes

Electro Static Discharge (ESD) has been a major cause of failures in electronic devices. As the electronic devices have moved towards high density SoCs accommodating ever increasing number of gates at lower process nodes, their vulnerability to ESD effects has only increased. Among the reasons for ESD failures in SoCs, device… Read More

Innovus: Cadence’s Next Generation Implementation System

Yesterday was the first day of CDNLive. There were three keynotes. The first was by Lip-Bu Tan, Cadence’s CEO (and the Chairman of Walden International that he will be the first to remind you). The most interesting tidbit was that Cadence now has over 1000 people working on IP and that it represents 11% of their revenue. Then… Read More

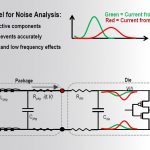

On-Chip Power Integrity Analysis Moves to the Package

Power regimes for contemporary SOC’s now include a large number of voltage domains. Rail voltages are matched closely to the performance and power requirements of various portions of the design. Indeed, some of the supply voltages are so low that the noise margins in these domains is exceedingly low. Higher voltage domains are… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era