With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

Electronic Design Automation

Synopsys to Acquire Atrenta

I was at the DAC kickoff this evening in the Intercontinental Hotel. I was talking to Dave DeMaria, the senior marketing guy at Synopsys and he told me of a couple of minor press releases due to hit the wire tomorrow morning, didn’t sound important enough to be blogworthy. Aart was there too although I didn’t speak to him.… Read More

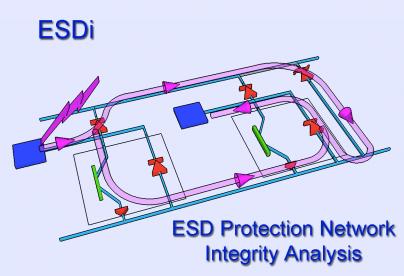

ESD Protection Network Checking is Difficult But Necessary

I’ve written before about anti-fuse non-volatile memory, where the gate oxide is intentionally damaged in order to create a readable bit of data, but this is what most circuit designers never want to have happen to their logic gates. However, since the advent of MOS transistors the issue of Electrostatic Discharge (ESD) and the… Read More

Vacationing with the Fabless Semiconductor Ecosystem!

The Design Automation Conference is the largest and most diverse event in the fabless semiconductor ecosystem. Next week in San Francisco you will see technology and people you have never seen before. You will benefit from the efforts of hundreds of thousands of semiconductor professionals like myself who have dedicated their… Read More

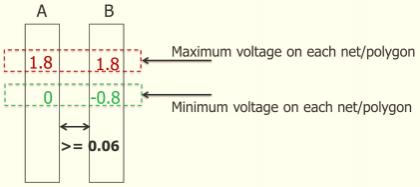

Automate those voltage-dependent DRC checks!

Because IC design and verification never gets simpler, verification engineers now have to comply with voltage-dependent DRC (VD-DRC) rules. What does this term mean, and what new challenges does it bring to the DRC task? I’d like to share what I learned during another water-cooler conversation with Dina Medhat, senior technical… Read More

Is Avago Chip Industry’s Cisco?

If Ford is a reference model for value chain in the Industrial Age, Cisco is the icon of the twenty-first-century digital economy. The networking gear maker, who achieved phenomenal growth with the rise of the Internet, has been remarkably successful in snapping up and integrating scores of companies for products it could not … Read More

The Transistor is the Foundation of TCAD to Signoff

At the most basic level, semiconductor design is all about transistors. Any report on a large microprocessor or mobile application processor is in awe about how many transistors it contains. Moore’s Law is all about the most economic way to manufacture transistors. Each process generation for the last decade and looking ahead… Read More

MIPI Beyond Mobile, Semiwiki Blogger Paper at #52DAC!

IoT or wearable: it’s fascinating to see how many articles, blogs, and comments have been posted about them during the last two years! IoT business potential is huge as are the number of possible applications. If we summarize the functions within a wearable system we can count:

[LIST=1]

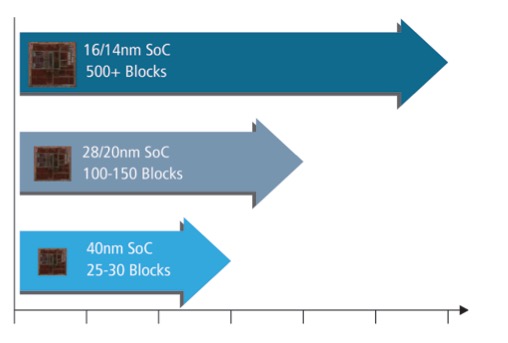

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

Even More Integration and Automation for ARM-based Designs

The attraction to an IP-based design methodology is that you can assemble an SoC from ready-made IP blocks, saving you valuable engineering development and verification time, while reducing risks from having to develop something from scratch and hoping that they meet industry standard specs. ARM is well known for supplying … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era