Advanced skill in auto repair, carpentry, plumbing, and similar trades often correlates to one factor. Knowing what you want to do is one thing – having the proper tool is another, and can make the difference. Many a job has extended from minutes to hours over the lack of the right tool at the right moment. Experienced mechanics and… Read More

Electronic Design Automation

What’s New with Static Timing Analysis

When I hear the phrase Static Timing Analysis (STA) the first EDA tool that comes to mind is PrimeTimefrom Synopsys, and this type of tool is essential to reaching timing closure for digital designs by identifying paths that are limiting chip performance. Sunil Walia, PrimeTime ADV marketing lead spoke with me by phone on Thursday… Read More

NVM IP now Available for On-Chip MCU Code

As of today NVM IP has been mostly used in SoC or IC to support very specific needs like analog trimming and calibration or encryption key integration for Digital Right Management (DRM) purpose. In other words small size (less than 1K-bit) few times programmable (FTP) NVM IP was enough to support these needs, thus most of the NVM IP… Read More

DNA Sequencing Eyes SoCs for Stability and Scale

DNA sequencing — which provides vital information on genetics study, forensics, diagnostics and therapies — has been an exclusive territory of high-end research labs with millions of dollars to spend because of the expensive chemical and optical equipment needed for research. That is changing, thanks to complex… Read More

Shorten the Learning Curve for High Level Synthesis

When chip designers moved from a gate-level design methodology to coding with RTL there was a learning curve involved, and the same thing happens when you move from RTL to High Level Synthesis (HLS) using C++ or SystemC coding. One great shortcut to this learning curve is the use of pre-defined library functions. I just heard about… Read More

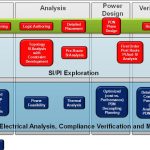

Sigrity Focuses on LPDDR4 Compliance Analysis in 2015 Release

It was back in July of 2012 that the acquisition of Sigrity by Cadence was announced. Although Cadence is a dominant player in both IC and board layout tools, they did not have an electromagnetic (EM) signal integrity solution in their portfolio. This acquisition marks a turning point for the EM/SI sector – tight integration… Read More

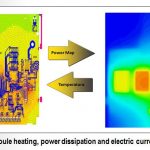

ANSYS Talks About Multi Physics for Thermal Analysis at DesignCon

ANSYS makes a big deal of being a multi-physics company. Still it has taken them a while to fully integrate Apache. Nevertheless it seems like there is a compelling argument for combining technologies to solve SOC design problems. Frankly most chip designers would be hard pressed to think of a reason for using computational fluid… Read More

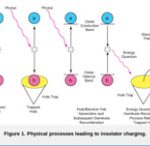

Silvaco TCAD Webinar

TCAD is a somewhat specialized area since not that many people design semiconductor processes compared to the number who design chips. Bit without TCAD there would be no chips. One area where the two domains intersect is that of SEE, where neutrons (mainly) can cause a flop or a memory bit to change. Since we live on a radioactive planet… Read More

30+ Years of Semiconductors – The base matters!

Although CMOS technology in semiconductors was patented in 1960s, commercial ICs and electronic systems based on CMOS ICs started picking up in 1970s, and the real growth with personal computer (PC) market took place in 1980s. Then Intelmicroprocessors started dominating the semiconductor market with increasing processing… Read More

Measuring Metastability

Measuring metastability is just 50 years old this year. In 1965 my colleague Tom Chaney took a sampling ‘scope picture of an ECL flip-flop going metastable. S. Lubkin had made mention of the phenomenon over a decade before that, but at that time most engineers were unaware of the phenomenon or did not believe it actually existed. … Read More

Weebit Nano Moves into the Mainstream with Customer Adoption