Did you know that by 2020 90% of cars will be connected to Internet? Great, but today, there are already more than 100 car models affected with security flaws (Source: theguardian.com, 2015). That 320 apps are installed on average smartphone device? It would be a complete success, but 43% of Android devices allow installation of… Read More

Electronic Design Automation

How to Overcome HW Project Release Nightmares

Is a software development release methodology a “square peg in a round hole” when it comes to hardware design? To answer this question we have to look at how exactly hardware design projects differ from their software counterparts. Intuitively we know they are fundamentally different. Let’s take a second to dig deeper to understand… Read More

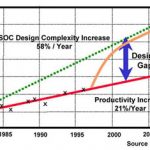

How to Solve the Business Gap in SEMI Industry?

This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced … Read More

Semiconductors and Conflict Minerals

Our semiconductor industry uses many different materials and chemicals in the production of chips, boards and electronic systems. But what should we do if the minerals like tantalum, tin, tungsten and gold are coming from the eastern provinces of the Democratic Republic of the Congo where armed bandits are forcing workers against… Read More

Auto Introspection

It is an indictment of our irrationality that our cars are now more health-conscious than we are. Increasingly safety-conscious readings of the ISO26262 standard now encourage that safety-critical electronics (anti-lock braking control for example) automatically self-test, not just at power-on but repeatedly as the car… Read More

Calibre in the Middle of Semiconductor Ecosystem

Albert Einsteinhad said, “In the middle of difficulty lies opportunity”. In today’s world dominated by technology, or I must say internet which has initiated collaborative information sharing, “leading from the middle” is the new mantra of life.… Read More

Variation Aware FinFETs are Critical!

As I mentioned in “EDA Dead Pool” acquisitions in our industry will continue at a rapid pace. The latest victim is 10 year old French company Infiniscale who was recently purchased by Silvaco. This was more of a “let’s put your product through our massive sales and support channel” kind of deal so it will be 1 + 1 = 3 accretive for sure.… Read More

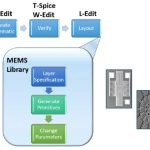

Mass customization coming to MEMS?

With the industry abuzz about the Apple purchase of a Maxim Integrated fab as a potential R&D facility for MEMS design, it begs the question: is creating a MEMS device that easy?

MEMS technology is approaching the same fork in the road where digital design encountered LSI four decades earlier. … Read More

Challenges in IP Qualification with Rising Physical Data

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

Freescale Semiconductor: The End of a Long Journey

“You don’t argue with success,” said Paul Galvin back in 1949 at the creation of a new venture that would eventually become known as Motorola Semiconductor Products Sector. He was referring to how Daniel E. Noble, one of Motorola’s top managers, had persuaded him to set up a small electronics research… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center