This is part 3 of a series of 4 on low power design, scheduled for September 21st at 10am. Kiran Vittal and Ken Mason will be discussing using the SpyGlass Power solutions (analysis and verification) to optimize power at RTL. Atrenta always had a leading position in this area; I expect a year following their acquisition by Synopsys,… Read More

Electronic Design Automation

Synopsys Webinar: MIPI Adoption Beyond Mobile, it’s now!

Some of the various MIPI specifications are now massively used in mobile (smartphone or tablet), especially the Multimedia related specs like Camera Serial Interface (CSI-2), Display Serial Interface (DSI) and D-PHY. You have to implement with CSI-2 or DSI controller a serial based physical interface, D-PHY specified up to… Read More

Pseudo random generator tutorial in VHDL (Part 3/3)

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

Pseudo random generator tutorial in VHDL (Part 2/3)

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

Pseudo random generator tutorial in VHDL (Part 1/3)

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

Five Things To See at DVCon India 2016

DVCon is an annual Design and Verification Conference that started out in Silicon Valley, then expanded by adding India as a new location. Our semiconductor design and verification world is global in stature, so if you’re living in the region then consider registering for this event held Thursday and Friday, September … Read More

Is Your Next Reality Going to be Augmented?

John Lennon reportedly once said “Reality leaves a lot to the imagination…” and now we have the technology to do something about making our reality a lot more imaginative. Unless you have been living under a rock (and there is nothing wrong with that – I just haven’t found the right rock myself) there is a LOT going on these days in the… Read More

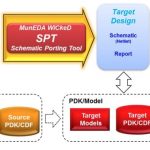

Three Steps for Custom IC Design Migration and Optimization

Popular companies designing smart phones, CPUs, GPUs and Memory components all employ teams of custom IC designers to create the highest performance chips that are as small as possible, and at the lowest costs. How do they go about doing custom IC design migration and optimization when moving from one process node to another one?… Read More

A new world of 10nm design constraints

Every time the industry transitions to a smaller process node IC design software undergoes extensive updates.

I talked to a couple of experts in physical design at Mentor Graphics about what is involved in making place-and-route software ready for a new node. This is what I learned from Sudhakar Jilla, the IC design marketing director… Read More

Embedded Product Development – Make vs Buy

Original Equipment Manufacturers (OEMs) face many questions before building any product. After they are convinced that there is a business potential in their new product, next comes the crucial stage of project execution. They aspire to build the product in-time, maybe before the competitors or better than the competing products,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center