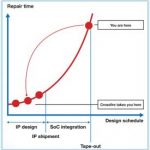

I was CTO at Atrenta, home of SpyGlass, for many years before the company was acquired by Synopsys, so I know a thing or two about IP quality, to paraphrase a popular commercial. The problem is that even in the best-run IP shops, errors happen. Sometimes they happen on simple changes, especially when you think “This IP has been very … Read More

Electronic Design Automation

3 in 1 Hardware Verification

Aldec has offered front-end EDA tools for over 30 years but may not be a familiar name to mainstream IC design engineers. That’s probably because for most that period they haven’t really targeted IC design. They have been much more focused on PC-based design for FPGAs particularly where requirements traceability has been important,… Read More

CEO Interview: Chouki Aktouf of Defacto Technologies

As a 30+ year semiconductor veteran I can tell you with 100% certainty that start-ups are the lifeblood of EDA. The mantra is “Innovate or Die!” and that is exactly what Defacto is doing. After more than 10 years of innovating in Design for Test at RTL, Defacto is now offering a complete EDA solution based on generic EDA… Read More

Optimizing Prototype Debug

In the spectrum of functional verification platforms – software-based simulation, emulation and FPGA-based prototyping – it is generally agreed that while speed shoots up by orders of magnitude (going left to right) ease of debug drops as performance rises and setup time increases rapidly, from close to nothing for simulation… Read More

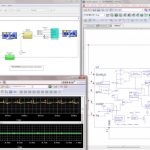

System-level Design for IoT and Automotive

Several years ago a former EDA co-worker went to work for MathWorks, so I started paying a lot more attention to this privately held company that is well known for the MATLAB language and analysis environment. Engineers at MathWorks have created a graphical environment called Simulink for both simulation and model-based design… Read More

Executive Interview: Vic Kulkarni of ANSYS

Having known Vic for many years, it is always great to spend time with him and catch up on what is happening inside the semiconductor ecosystem. As Senior Vice President and General Manager, RTL Power Business, at ANSYS in Silicon Valley, Vic spends a lot of time in the field with customers, partners, and at industry events so he has… Read More

Automotive Semiconductor Safety

One of the more telling trends in the semiconductor industry is the “fabless systems companies” transformation. Systems companies that used to buy chips are now making their own to better control the system they are designing: from the chip, package, PCB, the complete system. Apple is the best example as they are now one of the most… Read More

How to nail your PPA tradeoffs

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters… Read More

Protium for the win in software development

Cadence Design Systems is a long-standing provider in hardware emulation, but a relative newcomer to FPGA-based prototyping. In an upcoming lunch and learn session on November 11 in San Jose, Cadence teams will be outlining their productivity strategy. What’s different with their approach and why is this worth a lunch?… Read More

Keeping It Fresh with the Veloce Deterministic ICE App

In The Times They Are A Changin’ Nobel Laureate Bob Dylan advised us to “heed the call” of change or suffer the consequences. This couldn’t be more true, considering what design and verification engineers face every day in the midst of the technological revolution.

Change has never been so rapid. And it requires we constantly adapt.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center