Counting squares is a useful tool for calculating simple resistance in wires, but falls short in reality when wires deviate from ideal. Frequently the use of RC extraction tools for determining resistance in signal lines in digital designs can be effective and straightforward. However, there are classes of nets in designs that… Read More

Electronic Design Automation

SPIE Advanced Lithography and Synopsys!

SPIE is the premier event for lithography held in Silicon Valley and again Scotten Jones and I will be attending. EUV is generally the star of the show and this year will be no different now that TSMC has committed to EUV production in 2019.

Last year at SPIE, TSMC presented the history of EUV development from the beginning in 1985 as … Read More

Finding Transistor-level Defects Inside of Standard Cells

In the earliest days of IC design the engineering work was always done at the transistor-level, and then over time the abstraction level moved upward to gate-level, cell-level, RTL level, IP reuse, and high-level modeling abstractions. The higher levels of abstraction have allowed systems to be integrated into an SoC that can… Read More

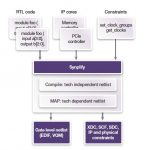

Four Steps for Logic Synthesis in FPGA Designs

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More

CEO Interview: David Dutton of Silvaco

Silvaco has undergone one of the most impressive EDA transformations so it was a pleasure to interview the man behind it. David Dutton’s 30+ year career started at Intel, Maxim, and Mattson Technology where he led the company’s turnaround and finished as President, CEO, and board member. David joined Silvaco as CEO… Read More

SoC Integration using IP Lifecycle Management Methodology

Small EDA companies often focus on a single point tool and then gradually over time they add new, complementary tools to start creating more of a sub-flow to help you get that next SoC project out on time. The most astute EDA companies often choose to partner with other like-minded companies to create tools that work together well,… Read More

Timing Closure Complexity Mounts at FinFET Nodes

Timing closure is the perennial issue in digital IC design. While the specific problem that has needed to be solved to achieve timing closure over the decades has continuously changed, it has always been a looming problem. And the timing closure problem has gotten more severe with 16/14nm FinFET SoCs due to greater distances between… Read More

Power Management Beyond the Edge

Power in IoT edge devices gets a lot of press around how to make devices last for years on a single battery charge, significantly through “dark silicon” – turning on only briefly to perform some measurement and shoot off a wireless transmission before turning off again. But we tend to forget that the infrastructure to support… Read More

Mentor Safe Program Rounds Out Automotive Position

Mentor has an especially strong position in the automotive space given their broad span of embedded, SoC, mechanical and thermal and system design tools. Of course, these days demonstrating ISO 26262 compliance is mandatory for semiconductor and systems suppliers, so EDA vendors need to play their part to support those suppliers… Read More

Qorvo and KeySight to Present on Managing Collaboration for Multi-site, Multi-vendor RF Design

Over the last several weeks I’ve been having a lot of discussions with colleagues around IP reuse and design data management. This led me to a discussion with Ranjit Adhikary, Marketing Vice President for ClioSoft.

ClioSoft is best known for their design collaboration software platform called SOS. They also sell an enterprise… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center