While some might have expected the exponential growth in design rules number and complexity to cool down a little, it looks as if these are only heating up more. The multiplicity of technology nodes, lithography options, , fundamental technology options (Bulk, FD-SOI, FinFET), different process flavors and specific applications,… Read More

Electronic Design Automation

Visual Quality

A few years ago, I started looking at data visualization methods as a way to make sense of large quantities of complex data. This is a technique that has become very popular in big data analytics where it is effectively impossible to see patterns in data in any other way. There are vast numbers of different types of diagram – treemap,… Read More

Cadence Design Systems @ #54DAC!

This year Cadence Design Systems is showcasing system design enablement in their booth, capitalizing on the industry shift from naked chip design to system level chip design. Apple started it with making the chips inside the iProducts as part of the system and now other systems companies are looking to take more control over their… Read More

Mentor a Siemens Business @#54thDAC

This year the Mentor booth will be quite interesting now that they are part of Siemens. I expect zero changes to their DAC presence but we shall see. It will certainly be good to see Wally again. More importantly, I will be afforded the opportunity to talk personally with both Wally Rhines, CEO of Mentor ANDChuck Grindstaff executive… Read More

Photonics at DAC – Integrated Electronic/Photonic Design Flow to be Presented at Cadence Theater

I recently wrote an article on SemiWiki talking about the integrated Electronic/Photonic Design Automation (EPDA) flow that is being developed by Cadence Design Systems, Lumerical Solutions and PhoeniX Software and how that flow is now expanding into the system level through SiP (system in package) techniques.

Up till recently,… Read More

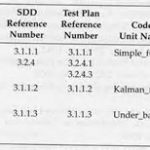

Simplifying Requirements Tracing

Requirements traceability is a necessary part of any top-down system specification and design when safety or criticality expectations depend on tightly-defined requirements for subsystems. Traceability in this context means being able to trace from initial documented requirements down through specification and datasheet… Read More

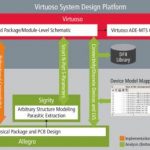

System Implementation Connectivity Verification and Analysis, Including Advanced Package Designs

Regular Semiwiki readers are aware of the rapid emergence of various (multi-die) advanced package technologies, such as: FOWLP (e.g., Amkor’s SWIFT, TSMC’s InFO); 2D die placement on a rigid substrate (e.g., TSMC’s CoWoS); and, 2.5D “stacked die” with vertical vias (e.g., any of the High Bandwidth Memory,… Read More

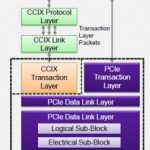

CCIX Protocol Push PCI Express 4.0 up to 25G

The CCIX consortium has developed the Cache Coherent Interconnect for Accelerators (X) protocol. The goal is to support cache coherency, allowing faster and more efficient sharing of memory between processors and accelerators, while utilizing PCIe 4.0 as transport layer. With Ethernet, PCI Express is certainly the most popular… Read More

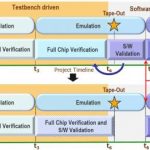

Listening to Veloce Customers: Emulation is Thriving

We have seen methodology shifts in our industry; emulation is going through a fundamental shift in usage, scope of the tasks, deployment, enterprise level and vertical market focus.… Read More

EDA Powered by Machine Learning panel, 1-on-1 demos, and more!

DAC is upon us again! The Design Automation Conference holds special meaning to me as it was the first technical conference I attended as a semiconductor professional, or professional anything for that matter. That was 33 years ago and I have not missed one since. This year my wife and I both will be walking the DAC floor and it would… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center