We have seen methodology shifts in our industry; emulation is going through a fundamental shift in usage, scope of the tasks, deployment, enterprise level and vertical market focus.

During the first half of 2017, the Mentor emulation team and our customers participated in the Mentor U2U Silicon Valley event, as well as the second annual Mentor/ARM Summit. What our customers talked about, in terms of how they use Veloce in their functional verification process, leads me to believe that the use of emulation continues to grow in ways that defy the historical view of emulation. Customer speakers included Cavium, Palo Alto, Samsung, Starblaze and Spreadtrum at U2U 2017, and ARM and Samsung at the Mentor/ARM Summit 2017. Below is a quick overview of those presentations.

U2U with Cavium: Cavium’s presentation titled, A Virtual Hybrid Approach for Verifying SDN Switches, was given by Nimalan Siva, senior manager, IC Engineering, and Ankit Anand, lead hardware engineer at Cavium SPG.

Anakit described how their verification flow, built around the Veloce emulation platform, deploys a virtual mode where two critical aspects of the virtual environment are of utmost importance.

- The VirtuaLAB Ethernet, a smart and powerful pre-silicon validation that supports up to 16 hosts, each with 64 MACs, providing a 1K of port density.

- A VirtuaLAB PCIe including a QEMU virtual machine running on the host network. The software stack processed by the QEMU included a PCIe Root Complex device driver, a guest OS like Fedora/Ubuntu/Windows, and user applications.

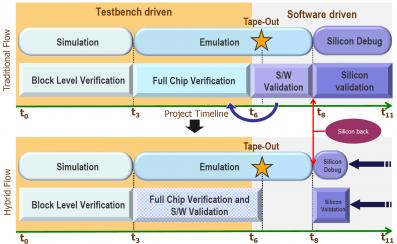

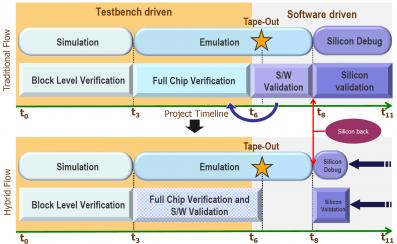

The results Anakit and Nimalan presented were significant. Including a project timeline shortened by several months because software validation was carried out during full chip verification, and silicon debug and validation only needed a couple of weeks after tape-out (figure 1).

U2U with Palo Alto Networks: Accelerating Universal Verification Methodology (UVM)-based Verification from Simulation to Velocewas given by Hung Truong, principal design verification engineer at Palo Alto Networks.

Hung started by setting the stage for augmenting simulation with emulation running more than 100k Ethernet traffic packets at full chip level in about one hour. He proceeded to describe the adoption of a UVM-based methodology and highlighted the changes required to move to emulation.

Hung concluded with an impressive summary of results.

- Reached speedup of more than 100X compared to simulation

- Rerun UVM-based tests in emulation with no/little change

- Some tests are too long for simulation, but ran on Veloce in less than an hour

- Performance numbers from a stress test compared to simulation

- Without fine tuning: 14X

- First round of fine tuning: 60X

- Another utilization of Veloce concurrency models: 100X

U2U with Starblaze:Bruce Cheng, ASIC architect, Starblaze Technology, gave a presentation titled Solid State Disk Controller Development based on Veloce VirtuaLAB and Software Model Solutions.

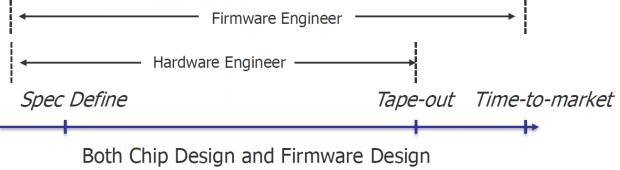

Starblaze adopted a software-driven chip design flow for their SSD controller design. In a software-driven design flow, firmware development starts at the same time as hardware design (figure 2). This is very different from a traditional hardware/software design flow where hardware and firmware development is serialized or pipelined.

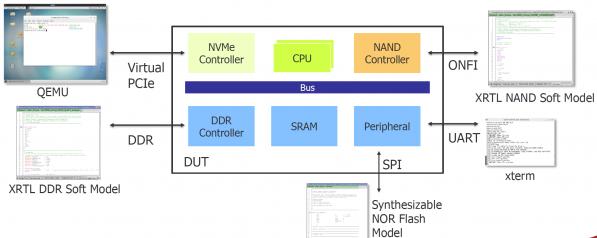

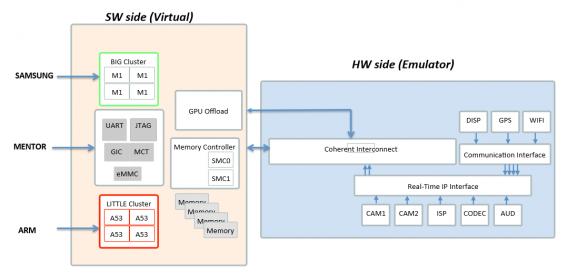

Starblaze’s verification and validation approach required a high-performance system that came as close as possible to the real chip environment, and provided powerful debug capabilities. The Veloce emulation platform was the ideal choice. When deployed in virtual mode, all peripherals exist in software models providing full control and visibility of the emulation environments, DUT, peripherals and interfaces (figure 3).

U2U with Samsung:The presentation titled, Virtual probe solution of Veloce for debugging of SoC software, was created by Kyuho Shim, Hyundon Kim, Seonil Brian Choi of Samsung S. LSI, and delivered by Russ Klein, technical director in the Mentor Emulation Division.

The Samsung presentation focused on the various methods to perform embedded software validation supported by Veloce. These include physical JTAG probes and virtual JTAG probes. Ultimately, the focus was on virtual probes, and the many advantages over physical probes. More specifically, maintaining a 1:1 speed ratio between the JTAG clock and the emulator clock.

U2U with Spreadtrum:Accelerate DFT Simulation, was presented by Seven Xu, Sr. staff engineer, and Kenneth Huang, senior DFT design engineer from Spreadtrum Corp.

Two types of DFT methods were emphasized, SCAN and MBIST. In deploying them, the Veloce DFT App addressed the following challenges:

- Gate-level DFT pattern simulation is a slow approach that dramatically impacts delivery schedule

- The need to identify patterns that lead to high-dynamic IR drop among the volume of patterns

- Debug must occur on the manufacturing floor via a tester that has limited visibility stretching debug time

In summary, the speaker presented two real case studies: GPU MBIST and SCAN.MBIST:Simulation took about 10 hours to process one test pattern. The Veloce DFT App provided:

-

[*=1]Easy bring up of the test environment in half-day.

[*=1]Run-time of ~3secs on one typical pattern: ~12,000X improvement over simulation

[*=1]Support for full visibility and file system database (FSDB) waveform dump

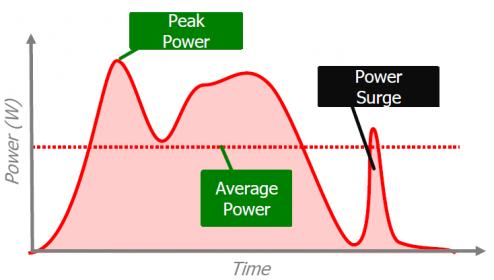

SCAN:The Veloce DFT App produced results in around one minute compared to four hours using simulation. When used together, the Veloce DFT App and Veloce Power App made it easy to identify peak power zones of activity during DFT emulation and generate the activity plot, and SAIF, FSDB waveforms (figure 4).

Mentor/ARM Summit 2017: A presentation titled Reckoning GPU Power with Velocewas given by Pranab Saharia, Senior Engineering, ARM.

Pranab gave an overview of the primary reasons ARM uses emulation. To accelerate verification, system-level debug, validation of GPU configuration and software validation. The majority of the presentation looked at how Veloce Power App is used to analyze and debug power issues.

Mentor/ARM Summit 2017: Nasr Ullah, Senior Director of Performance-Power Architecture, Samsung Austin R&D Center, SARC inspired the attendees with a presentation titled Hybrid Simulation-Emulation, The Potential and the Promise.

Nasr began by highlighting the importance of a completely integrated flow for semiconductor design—from architecture (modeling) to design and verification (RTL) to manufacture (silicon).

During the architectural to RTL design and verification stages, there is great value in having the tools and methodologies that ensure correlation from one stage to the next A hybrid simulation-emulation is part of Samsung’s approach to make this happen.

Simulation-Emulation Usage Domains

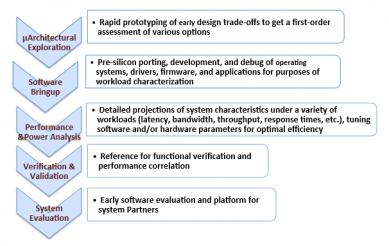

- Each model individually, or combined with other models in a co-simulation-emulation environment can be applied to multiple domains (figure 5).

Nasr then covered the important hybrid use requirements that make a co-simulation-emulation environment a powerful approach for verification.

- Architectural exploration platform

- Construction IDE for rapid prototyping of both systems and devices

- Reusable model libraries

- Highly configurable and parameterized

- Variety of input sources

- Rich data visualization feature

- System validation platform

- Reference-grade precision and accuracy

- Integration with RTL models

- VCD/waveform signal views

- Ability to explore system configurations

- Most components match the logic

To close the presentation, Nasr gave a look into the potential upside of a hybrid model and how using this model can be achieved.

- A hybrid model combines both virtual models with emulated models within the same environment

- Users can potentially switch from the virtual models to emulated models to analyze specific areas of interest in the application lifetime.

Conclusion

It is really fulfilling to see a wide variety of new emulation use models, with real life production data, shared at public forums. The Veloce platform continues to be the “emulator of choice” in the Networking segment because of its superior co-model channel. In the Storage space, Veloce’s virtual attributes are a game changer to accelerate the design and verification of complex SSD devices.

The new paradigm in HW/SW debug as presented by Nasr Ullah from SARC is opening new doors to usage at a much higher-level abstraction, and much sooner in the design cycle. In addition, in every market segment, Veloce DFT App is gaining momentum and usage because the value proposition is undisputable and customers understand it well. There is no doubt that it is a very exciting time to be in the Emulation space.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.