Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis,… Read More

Electronic Design Automation

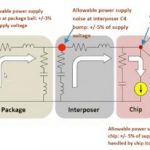

Power Integrity from 3DIC to Board

The semiconductor industry has built decades of success on hyper-integration to increase functionality and performance while also reducing system cost. But the standard way to do this, to jam more and more functionality onto a single die, breaks down when some of the functions you want to integrate are built in different processes.… Read More

Semiconductor Device Physics, Lab in a Box

One of my favorite classes in college was the lab exercise, mostly because we actually got to use real electronics and then measure something, finally writing it up in our lab notebooks. The issue today is that a college student taking Electrical Engineering probably doesn’t have much access to 10nm FinFET silicon for use… Read More

Is there anything in VLSI layout other than “pushing polygons”?

As I travel a lot in the last 15 years and visited customers as well as friends I was many times invited to talk to the Layout teams. The main purpose is always to encourage automation. So I developed a presentation related to market trend, technology trends, and latest tools advancements. In many cases I present updates from DAC (Design… Read More

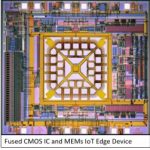

Fusing CMOS IC and MEMS Design for IoT Edge Devices

In my 34 years in IC and EDA, it never ceases to amaze me as to how ingenious designers can be with what is given them. Mentor, a Siemens business, has released a wonderful white paper that is proof of this yet again. The white paper steps through how one of their customers, MEMSIC, used the Tanner tool suite to develop a combination CMOS… Read More

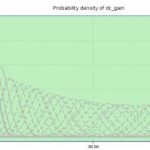

Solido Debuts New ML Tool at TSMC OIP!

The TSMC OIP Ecosystem Forum is upon us and what better place to debut a new tool to prevent silicon failures. Solido Design Automation just launched its latest tool – PVTMC Verifier – and will be demonstrating it in their booth at OIP. This is the third product that was developed within its Machine Learning Labs and is… Read More

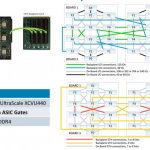

Webinar: Aiding ASIC Design Partitioning for multi-FPGA Prototyping

The advantages of prototyping a hardware design on a FPGA platform are widely recognized, for software development, debug and regression in particular while the ultimate ASIC hardware is still in development. And if your design will fit into a single FPGA, this is not an especially challenging task (as long as you know your way … Read More

Breakfast with Aart de Geus and the Foundries!

Being the number one EDA and the number one IP company does have its advantages and the resulting foundry relationships are a clear example. One of the DAC traditions that I truly enjoy is the Synopsys foundry breakfasts. Not only does Synopsys welcome scribes, they reserve a table up front for us and Synopsys CEO Aart de Geus has been… Read More

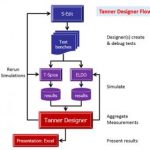

Project Management Tools for Analog IP Verification

Large SoC design teams typically have a cadre of project managers to oversee all facets of functional verification — e.g., specification, reviews, directed testbench development, automated (pseudorandom) testcase generation, HDL coverage measurement and reporting, and bug identification/tracking database management.… Read More

Webinar: Mobile Device Companies Get New Sensor Interconnect Standard

I’ve been a mobile device user since the 1980’s when the Motorola brick phone was introduced, so I’ve seen an increasing amount of sensors added to each new generation of mobile phones over the years. One big challenge to both sensor companies and fabless semiconductor companies designing SoCs for mobile devices… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center