Periodically Mentor does us all a big favor by commissioning a survey of verification engineers across the world to illuminate trends in verification. This is valuable not only to satisfy our intellectual curiosity but also to help convince managers and finance mandarins that our enthusiasm to invest in new methods and tools … Read More

Electronic Design Automation

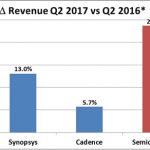

Semiconductor and EDA 2017 Update!

It really is an exciting time in semiconductors. The benchmarks on the new Apple A11 SoC and the Nvidia GPU are simply amazing. Even though Moore’s Law is slowing, the resulting chips are improving well above and beyond expectations, absolutely.

As I have mentioned before, non-traditional chip companies such as Apple, Amazon,… Read More

Walden Rhines on the Automotive Electronics Landscape

Mentor President and CEO Walden Rhines gave a comprehensive overview of the automotive electronics landscape at the Mentor Integrated Electrical Solutions Forum (IESF) in Plymouth, Mich., this week. A key focal point of Rhines’ comments was the twin industry disruptors: EVs and AVs.

A Texas Instruments alum, Rhines described… Read More

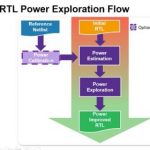

Clock Gating Optimization

You can save a lot of power in a design by gating clocks. For much of the time in a complex multi-function design, many (often most) of the clocks are toggling registers whose input values aren’t changing. Which means that those toggles are changing nothing functionally yet they are still burning power. Why not turn off those clock… Read More

IoT SoCs Demand Good Data Management and Design Collaboration

Design data management has always been important. Board designers have known this for decades as they had to have ways to keep all their discreet components organized and understood. Sourcing components is not easy as it means hours of reading and reviewing specifications, finding reliable sourcing partners and understanding… Read More

Open Silicon Delivers Silicon-Verified HBM2 IP-Subsystem on TSMC 16nm FF+

Open Silicon hosted a webinar today focusing on their High Bandwidth Memory (HBM) IP-subsystem product offering. Their IP-subsystem is based on the HBM2 standard and includes blocks for the memory controller, PHY and high-speed I/Os, all targeted to TSMC 16nm FF+ process. The IP-subsystem supports the full HBM2 standard with… Read More

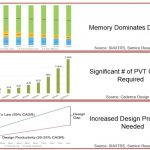

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

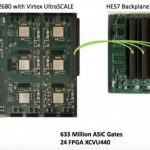

Partitioning for Prototypes

I earlier wrote a piece to make you aware of a webinar to be hosted by Aldec on some of their capabilities for partitioning large designs for prototyping. That webinar has now been broadcast and I have provided a link to the recorded version at the end of this piece. The webinar gets into the details of how exactly you would use the software… Read More

ATopTech is Back!

One of the biggest surprises at the TSMC OIP Forum last week was the reappearance of bankrupt EDA vendor ATopTech. I spoke with former ATopTech CEO and now Avatar IS President Jue-Hsien Chern at OIP. As a survivor of several EDA legal battles myself, I understand what ATopTech went through and I am thoroughly impressed that they had… Read More

Webinar: Signoff for Thermal, Reliability and More in Advanced FinFET designs

In automotive applications, advanced FinFET processes are great for high levels of integration and low power. But they also present some new challenges in reliability signoff. Ansys will be hosting a webinar to highlight the challenges faced by engineers trying to ensure thermal, electromigration (EM) and electrostatic discharge… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center