Being new in Ottawa and trying to get some momentum towards automation in full custom layout I was telling industry people that I am interested to work with everybody to move this agenda forward. My Director of Engineering at that time, Peter Gillingham, took me to visit Carleton University in Ottawa. One of his professor friends,… Read More

Electronic Design Automation

Webinar: ISO 26262 and DO-254: Achieving Compliance to Both

It’s near-impossible to read anything today about electronic design for cars without running into the ISO 26262 standard. If you design airborne electronic hardware, you’re likely very familiar with the DO-254 standard. But what do you do if you want to design a product to serve both markets? It looks like aircraft makers are increasingly… Read More

Bicycles, Electronics and CES 2018

I’m an avid road bike enthusiast having just completed my 2017 goal of 13,000 miles, so follow me on Strava if you want to see the routes and photo adventures I have in Oregon. In the photo below I’m the guy in the middle with the Portland Velojersey on and we’re in a parking lot just 2 blocks away from Intel’s… Read More

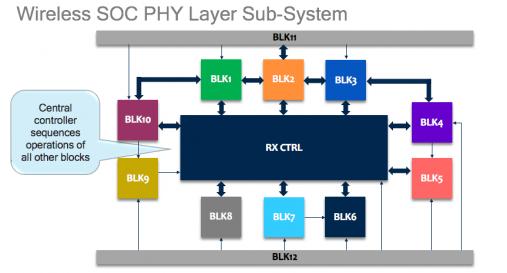

System Level Formal

Two recently announced vulnerabilities in major processor platforms should remind us that bugs don’t organize themselves to appear only in domains we know how to test comprehensively. Both Meltdown and Spectre (the announced problems) are potential hardware system-level issues allowed by interactions between speculative… Read More

Semiconductor Devices Transforming the World

As we begin another new year we begin another semiconductor conference cycle starting with SEMI ISS on January 15–18 at the Ritz-Carlton in Half Moon Bay California. This conference really sets the tone for the year and gives us a place to start thinking, acting, and reacting. This year it is all about the electronic devices we have… Read More

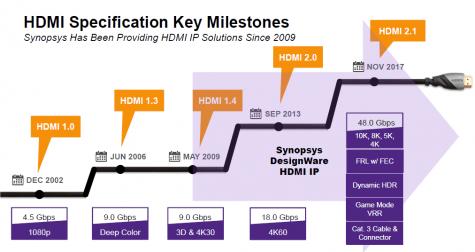

HDMI 2.1 Delivers 48.0 Gbps & Supports Dynamic HDR

You may or may not have bought HDMI-equipped device for black Friday or during year end break, but you TV set (or/and you PC) are certainly HDMI-powered, like the 750 million HDMI-equipped devices sold in 2016. In fact, cumulated shipment of HDMI-equipped devices has reached 6 BILLION since the protocol introduction in 2003! HDMI… Read More

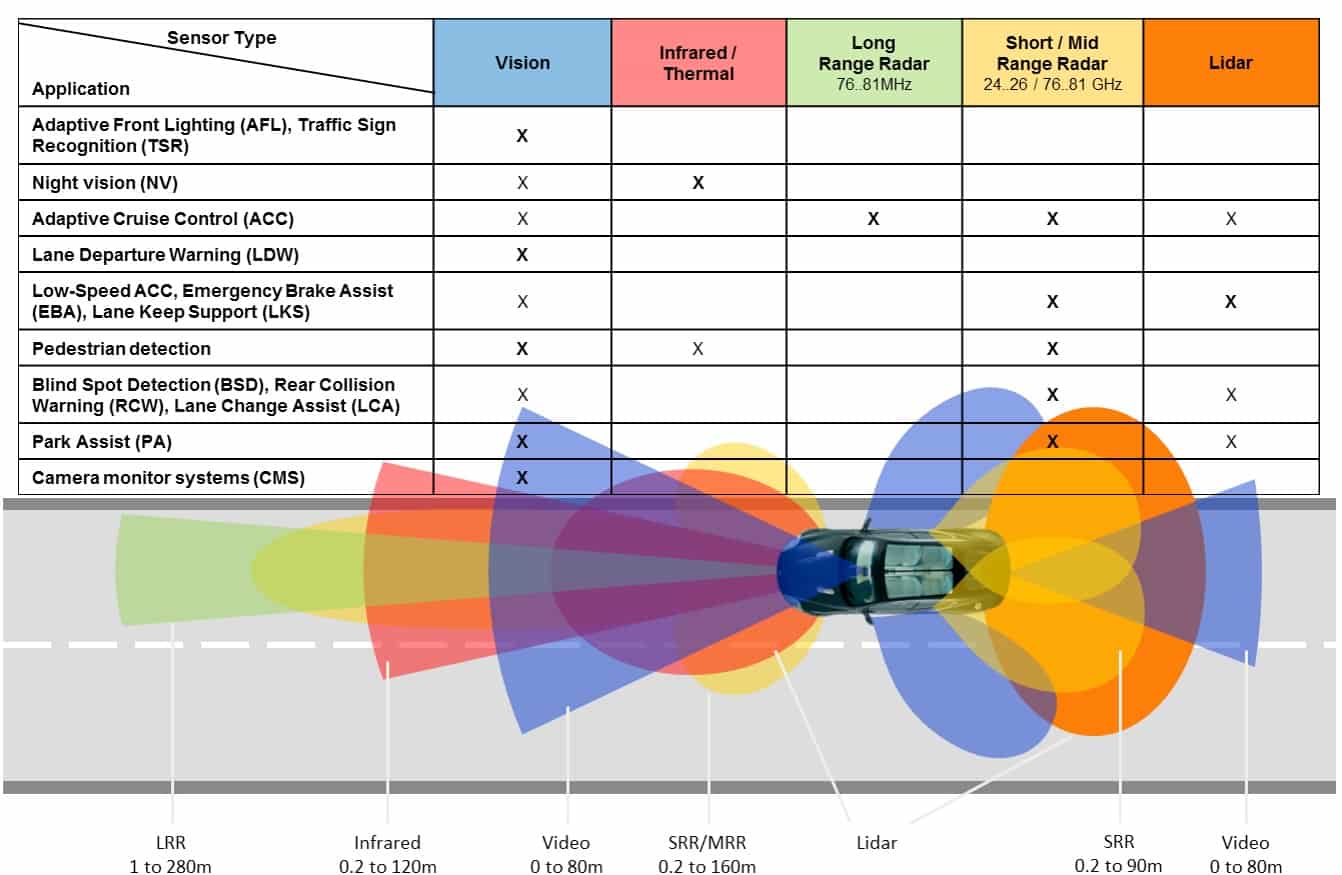

Autonomous Vehicles Upending Automotive Design Process

The automotive industry has a history of bringing about disruptive technological advances. One only needs to look at the invention of the assembly line by Henry Ford to understand the origins of this phenomenon. Today we stand on the brink of a massive change in how cars operate and consequently how they are built. A number of automotive… Read More

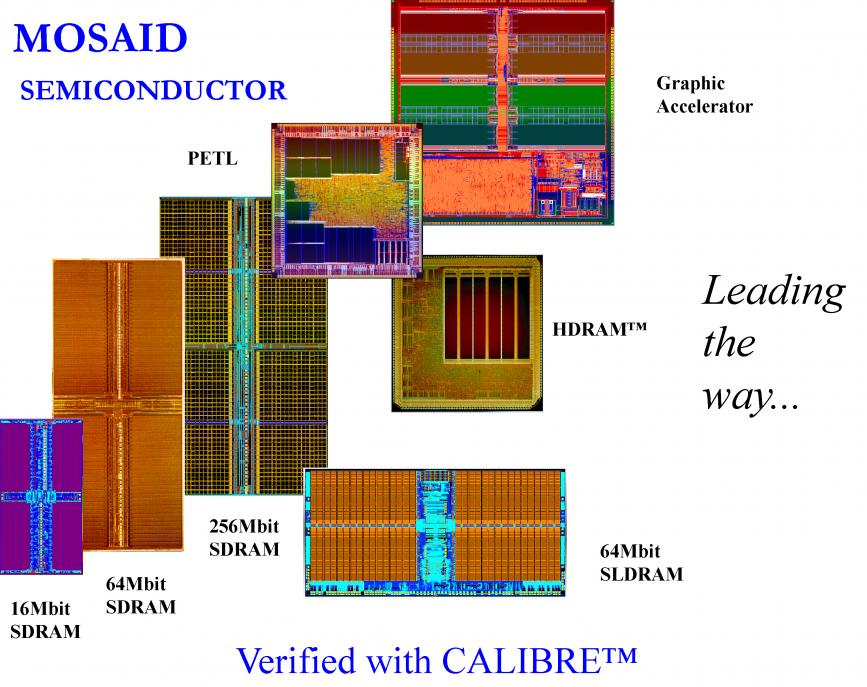

A Picture is worth a 1,000 words

Semiconductor IP re-use is a huge part of the productivity gains in SoC designs, so instead of starting from a clean slate most chip engineers are re-using cells, blocks, modules and even sub-systems from previous designs in order to meet their schedule and stay competitive in the market place. But what happens when you intend to… Read More

Using Sequential Testing to Shorten Monte Carlo Simulations

When working on an analog design, after initial design specs have been met, it is useful to determine if the design meets specs out to 3 or 4 sigma based on process variation. This can serve as a useful step before going any further. It might not be a coincidence that foundries base their Cpk on 3-sigma. To refresh, Cpk is the ratio of the… Read More

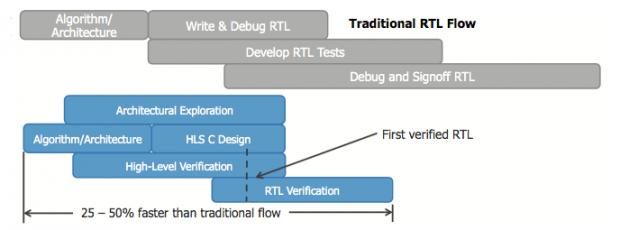

HLS Rising

No-one could accuse Badru Agarwala, GM of the Mentor/Siemens Calypto Division, of being tentative about high-level synthesis. (HLS). Then again, he and a few others around the industry have been selling this story for quite a while, apparently to a small and not always attentive audience. But times seem to be changing. I’ve written… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center