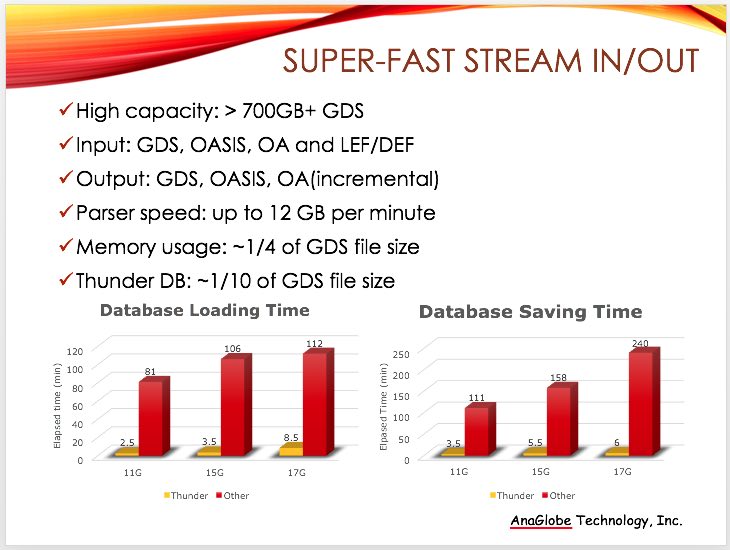

During the design cycle as tape out approaches, time pressure usually goes up dramatically. To make matters worse the design itself is much larger, because all the block level work is done and there is a requirement to work with the entire database. It feels like it’s time to put aside the garden trowel and start using a steam shovel.… Read More

Electronic Design Automation

Fractal Technologies Joins TSMC Open Innovation Platform EDA Alliance

In case you missed it, Fractal is now officially part of the TSMC EDA Alliance. Fractal Crossfire is the leading IP and Library QA tool used by TSMC and many of TSMC’s customers so this is for the greater IP good, absolutely. Fractal has also released a new white paper “Setup Generation for Fractal Crossfire” that we can talk about but… Read More

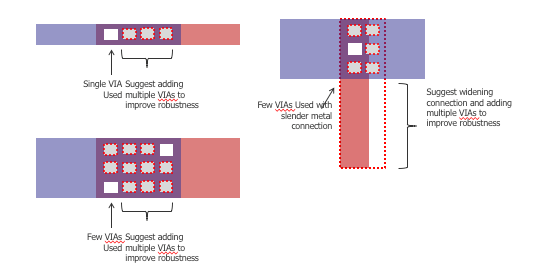

Foundry Partnership Simplifies Design for Reliability

This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures,… Read More

Mentor Emulation Platform Now available on Amazon Web Services

Emulation is a hotly contested EDA market segment (which is being won by Mentor) and EDA in the Cloud is a trending topic so putting the two together is a very big deal, absolutely.

The following is a quick email Q&A with Jean-Marie Brunet, Director of Marketing, Emulation Division, Mentor, a Siemens Business. If you have other… Read More

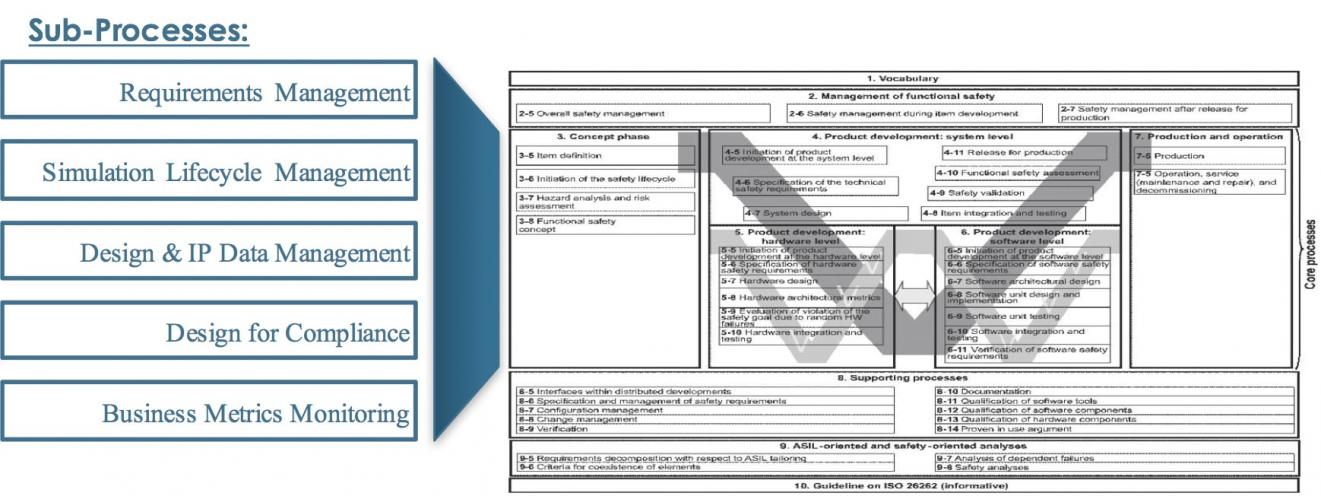

ISO 26262 Traceability Requirements for Automotive Electronics Design

Reading the many articles on SemiWiki and other publications we find experts talking about the automotive market, mostly because it’s in growth mode, has large volumes and vehicles consume more semiconductors every year. OK, that’s on the plus side, but what about functional safety for automotive electronics?… Read More

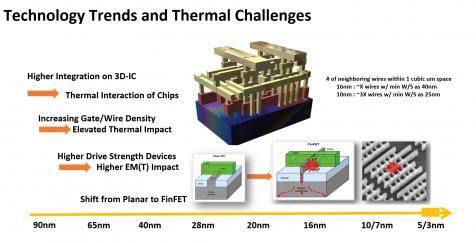

Thermal and Reliability in Automotive

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More

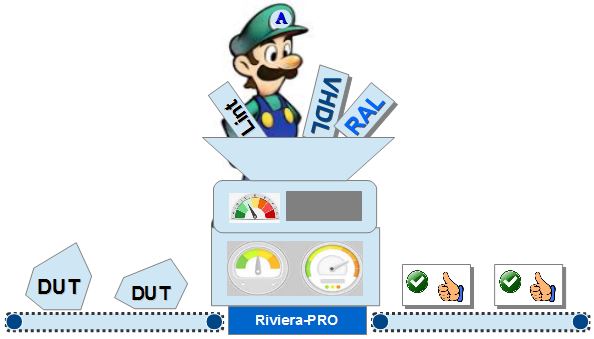

RAL, Lint and VHDL-2018

Functional verification is a very effort intensive and heuristic process which aims at confirming that system functionalities are meeting the given specifications. While pushing cycle-time improvement on the back-end part of this process is closely tied to the compute-box selection (CPU speed, memory capacity, parallelism… Read More

DRC is all About the Runset

EDA companies advertise their physical verification tools, aka DRC (Design Rule Check), mostly in terms of specific engine qualities such as capacity, performance and scalability. But they do not address an equally if not more important aspect: the correctness of the actual design rules.

Put bluntly: It’s not about how… Read More

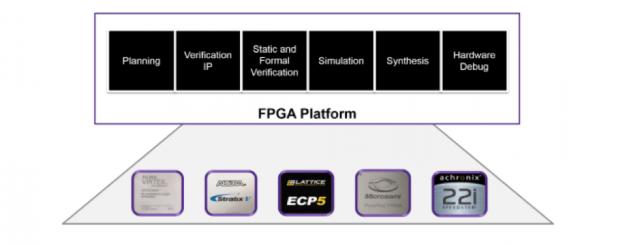

When FPGA Design Looks More Like ASIC Design

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

John Lee: Market Trends, Raising the Bar on Signoff

I talked to John Lee (GM of the ANSYS Semiconductor BU) recently about his views on market trends and the ANSYS big-picture theme for DAC 2018. He set the stage by saying he really liked Wally’s view on trends (see my blog on Wally’s keynote at U2U). John said these confirm what he is seeing – a trend to specialization, some around… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center